高性能32位內核與基于微控制器存儲架構的集成

改進的設計

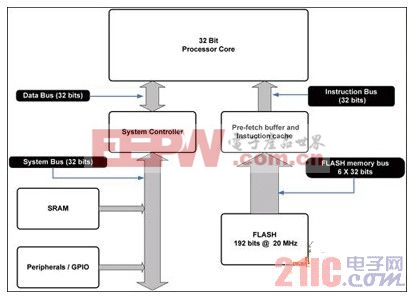

我們現在可以把學到的知識應用于我們系統的第一個框圖,并從預取/指令高速緩存緩沖器系統提供的增益中獲益。詳見以下的圖 3。

圖3 改進的32位內核設計

與之前的16位設計相比,新設計能夠以三倍的速度(120 MHz / 2.0 CPI(預取)/ 20 MHz(16 位時鐘)執行指令,通過適當選擇最終指令高速緩存的大小,很容易就能實現非常接近單等待狀態閃存系統運行的性能。

雖然指令預取緩沖器是一種簡單的實現,但它通過屏蔽閃存和 32 位內核執行速度之間的存取時間差異,顯著地改善了系統吞吐量。預取緩沖器是一個非常簡單的設計,只需要很少的額外邏輯。大部分額外邏輯與擴展閃存系統和預取緩沖存儲器之間的通道有關。設計的簡單有利于它完全透明地展示給軟件程序員,他們只需允許或禁用該功能就可以了。

形式指令高速緩存是一種更復雜的解決方案,需要至少與預取緩沖器相同數量的額外邏輯電路,以及管理指令高速緩存正常運行的額外邏輯電路。設計人員需要分析 MCU 運行的典型應用,以確定能夠最好地平衡性能和成本的高速緩存大小。當然,指令高速緩存部署更為昂貴,但是在許多情況下,系統實現的性能可達到 0 等待狀態系統,對性能產生顯著的積極作用。軟件程序員還必須了解與指令高速緩存有關的一些基本控制和維護問題,但是在大多數情況下,它們可以一勞永逸地運行,只是在系統初始化時才需要執行。

只用新的 32 位器件直接替代現有的 8 位或 16 位內核是不夠的。芯片設計人員還必須調整和改進整個 MCU 設計,以適應高性能、高速度 32 位內核的新要求。我們需要這樣的調整來確保新的 32 位內核能夠釋放最高性能。采用預取緩沖器和指令高速緩存是改進微控制器設計的兩個直接途徑,微控制器與 32 位內核和現有存儲器技術直接相關。

評論