基于達(dá)芬奇技術(shù)的數(shù)字視頻系統(tǒng)設(shè)計與實現(xiàn)

摘要:達(dá)芬奇技術(shù)是業(yè)界第一款集成了DSP 處理器、軟件、工具以及技術(shù)支持的綜合型解決方案系列,非常適用于開發(fā)各種優(yōu)化的數(shù)字視頻終端設(shè)備。本文介紹了一種基于達(dá)芬奇技術(shù)的數(shù)字視頻系統(tǒng)設(shè)計方案。詳細(xì)闡述了該系統(tǒng)的總體架構(gòu)、視頻部分功能、電源設(shè)計和軟件實現(xiàn)。

本文引用地址:http://www.czjhyjcfj.com/article/167050.htm引 言

在數(shù)字視頻創(chuàng)新已經(jīng)成為數(shù)字信息產(chǎn)業(yè)熱點的今天,數(shù)字視頻系統(tǒng)的設(shè)計方法不斷提高,數(shù)字視頻系統(tǒng)的復(fù)雜度已經(jīng)遠(yuǎn)遠(yuǎn)超過以往任何時候。達(dá)芬奇技術(shù)成功實現(xiàn)數(shù)字視頻需要四大要素的最新進(jìn)步,即:處理器、開發(fā)工具、軟件以及系統(tǒng)專業(yè)技術(shù)。由于能夠在集成這四種要素的平臺中實現(xiàn)數(shù)字視頻、音頻、語音與話音技術(shù),因此達(dá)芬奇技術(shù)可以為數(shù)字視頻的當(dāng)前變革打下基礎(chǔ)。

本設(shè)計是在一塊60*60mm 的PCB板上來完成視頻的采集、處理與顯示。由攝像頭采集的視頻圖像經(jīng)由解碼器轉(zhuǎn)換成達(dá)芬奇處理器能夠處理的格式,在Codec Engine 中實現(xiàn)H.264 、MPEG-4編解碼,在LCD液晶屏上最高能達(dá)到1280*720 分辨率下30fps(幀/每秒)流暢顯示。這樣的數(shù)字視頻系統(tǒng)能達(dá)到尺寸小,功能強,設(shè)計靈活,實用性廣的優(yōu)點。

1. 1.系統(tǒng)的總體架構(gòu)及工作原理

2. 1.1 TMS320DM6446 器件總攬 達(dá)芬奇處理器TMS320DM6446 是基于業(yè)界最高性能的DSP平臺―TI TMS320C6000 由ARM926EJ-S 內(nèi)核、TMS320C64x+ DSP 內(nèi)核、系統(tǒng)控制、視頻處理子系統(tǒng)(VPSS)、電源管理、外部存儲器接口、外圍控制模塊等功能模塊組成。

TMS320DM6446 中的ARM926EJ-S 內(nèi)核具有16KB 指令和8KB 數(shù)據(jù)Cache 及16KB ROM 和16KB RAM 。TMS320C64x+ DSP 內(nèi)核具有32KB L1 程序R A M / C a c h e 、8 0 K B L1 數(shù)據(jù)R A M /Cache 及64KB L2 RAM/Cache 。具有DDR2 內(nèi)存控制器;64 通道增強型DMA 控制器;串行端口(3 個UART、I2C、SPI、音頻串口);3 個64 位通用定時器;10/100M 以太網(wǎng);USB2.0 端口;3 個PWM 端口;多達(dá)71 個通用I/O 口;支持MMC/SD/CF 卡等。系統(tǒng)控制模塊提供了看門狗、中斷控制器、電源管理控制器、復(fù)位控制器及2 個片上振蕩器。視頻處理子系統(tǒng)(VPSS) 有用于視頻輸入的視頻前端輸入(VPFF) 接口由CCD 控制器(CCDC), 預(yù)處理器、柱狀模塊、自動曝光/白平衡/聚焦模塊(H3A)和寄存器組成;和用于視頻輸出的視頻后端輸出(VPBE)接口由屏幕菜單式調(diào)節(jié)器(OSD)、視頻編碼器(VENC)和四路10bit DACs 組成。

1.2 系統(tǒng)的硬件組成及工作原理

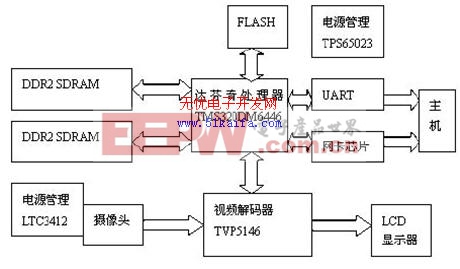

整個數(shù)字視頻系統(tǒng)采用的是由達(dá)芬奇處理器(TMS320DM6446)、DDR2 SDRAM 、NAND FLASH、視頻解碼器TVP5146 、電源管理芯片TPS65023,LTC3412 加上外圍接口芯片的方案。視頻解碼器把CCD攝像頭傳過來的模擬視頻信號進(jìn)行模/數(shù)轉(zhuǎn)換,變成符合ITU-BT.656 標(biāo)準(zhǔn)的數(shù)字視頻信號,然后將數(shù)字視頻信號傳到達(dá)芬奇處理器的視頻處理子系統(tǒng)的前端進(jìn)行預(yù)處理經(jīng)過Codec Engine 編解碼后送到視頻處理子系統(tǒng)的后端,直接輸出數(shù)字視頻信號到顯示終端上或是通過四路54MHz 的DACs來提供NTSC/PAL制式的模擬視頻輸出。DM6446 上的ARM端主要做為控制器來控制視頻解碼芯片和外圍接口芯片,DSP端主要負(fù)責(zé)視頻編解碼工作。系統(tǒng)硬件框圖如圖1所示

圖1 系統(tǒng)硬件框圖

1. 2.視頻部分的硬件結(jié)構(gòu)及其分析

2. 2.1 視頻采集與解碼

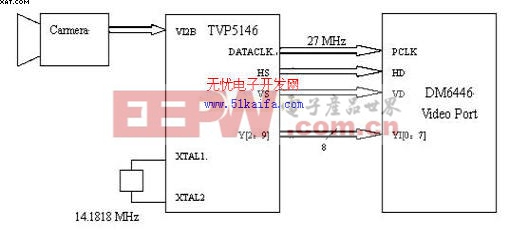

本設(shè)計選用TI公司的視頻解碼芯片TVP5146 完成從模擬到數(shù)字視頻的轉(zhuǎn)換。TVP5146 允許10路模擬視頻輸入,具有4路10bit A/D 轉(zhuǎn)換器;場同步信號VS,行同步信號HS,奇偶場信號FID,時鐘輸出信號DATACLK 等都由引腳直接引出,省去同步時鐘電路的設(shè)計。

TVP5146 上的Y[9:2]為輸出的亮度視頻信號,DATACLK 為行鎖定系統(tǒng)的輸出時鐘,像素時鐘頻率為27MHz, 用來同步數(shù)據(jù)采集,HS為行同步信號,VS為場同步信號分別與達(dá)芬奇處理器DM6446 視頻端口對應(yīng)的信號相連接。HS的高電平表示一行有效采樣點個數(shù),VS 的高電平表示一場有效信號,對于NTSC 制信號,單場為243 行, 奇偶場信號FID為1 時,表示當(dāng)前為奇數(shù)場,為0 表示偶數(shù)場。視頻解碼芯片與DM6446 的接口電路如圖2所示。

圖2 視頻前端模塊接口

評論