基于FPGA 的VGA 圖形控制器的實(shí)現(xiàn)方法

引言

本文引用地址:http://www.czjhyjcfj.com/article/161995.htmVGA(視頻圖形陣列)作為一種標(biāo)準(zhǔn)的顯示接口得到廣泛的應(yīng)用。利用FPGA 芯片和EDA 設(shè)計(jì)方法,可以因地制宜,根據(jù)用戶的特定需要,設(shè)計(jì)出針對(duì)性強(qiáng)的VGA 顯示控制器,不僅能夠大大降低成本,還可以滿足生產(chǎn)實(shí)踐中不斷變化的用戶需要,產(chǎn)品的升級(jí)換代方便迅速。

在本設(shè)計(jì)中采用了Altera 公司的EDA 軟件工具Quartus II ,并以ACEX系列FPGA 的器件為主實(shí)現(xiàn)硬件平臺(tái)的設(shè)計(jì)。

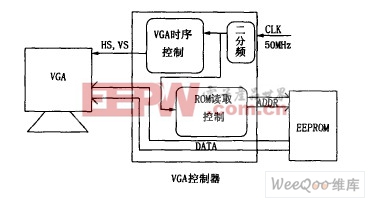

根據(jù)自頂向下的程序設(shè)計(jì)思想,采用模塊化設(shè)計(jì),我們對(duì)VGA 圖形控制器進(jìn)行功能分離并按層次設(shè)計(jì)。利用VHDL 硬件描述語言逐一對(duì)每個(gè)功能模塊進(jìn)行描述,并逐個(gè)通過編譯仿真,最后下載到硬件平臺(tái)調(diào)試。本設(shè)計(jì)的VGA 控制器主要由以下模塊組成:VGA 時(shí)序控制模塊、分頻模塊、漢字顯示模塊、圖像控制模塊、ROM讀取模塊等,如圖1 所示。

圖1 基于FPGA 的VGA 圖形控制系統(tǒng)框圖

2 主要功能模塊設(shè)計(jì)

2. 1 VGA 時(shí)序控制模塊

VGA 時(shí)序控制模塊是整個(gè)顯示控制器的關(guān)鍵部分,最終的輸出信號(hào)行、場同步信號(hào)必須嚴(yán)格按照VGA 時(shí)序標(biāo)準(zhǔn)產(chǎn)生相應(yīng)的脈沖信號(hào)。對(duì)于普通的VGA 顯示器, 其引出線共含5 個(gè)信號(hào): G,R ,B (3 基色信號(hào)) ,HS(行同步信號(hào)) ,VS(場同步信號(hào)) 。在5個(gè)信號(hào)時(shí)序驅(qū)動(dòng)時(shí),VGA 顯示器要嚴(yán)格遵循“VGA工業(yè)標(biāo)準(zhǔn)”, 即640 Hz ×480 Hz ×60Hz 模式。

對(duì)于VGA 顯示器,每個(gè)像素點(diǎn)的輸出頻率為25. 175MHz ,因此采用50MHz 的時(shí)鐘信號(hào),經(jīng)過二分頻模塊,得到25MHz 的輸入時(shí)鐘脈沖。依據(jù)VGA 時(shí)序標(biāo)準(zhǔn),行同步信號(hào)HS ,行周期為31. 78μs ,每顯示行包括800 點(diǎn),其中640 點(diǎn)為有效顯示區(qū),160 點(diǎn)為行消隱區(qū),每行有一個(gè)脈沖,該脈沖的低電平寬度為3. 81μs (即96 個(gè)脈沖) ; 場同步信號(hào)VS ,場周期為16.683ms ,每場有525 行,其中480 行為有效顯示行,45 行為場消隱區(qū),每場有一個(gè)脈沖,該脈沖的低電平寬度為63μs (2 行)。

圖2 VGA 行掃描、場掃描的時(shí)序圖

依據(jù)這個(gè)標(biāo)準(zhǔn),把輸入的25MHz 時(shí)鐘脈沖按照對(duì)應(yīng)的像素點(diǎn)數(shù)和掃描行數(shù)進(jìn)行分頻處理,可以得到最后符合時(shí)序要求的行頻率和刷新頻率。

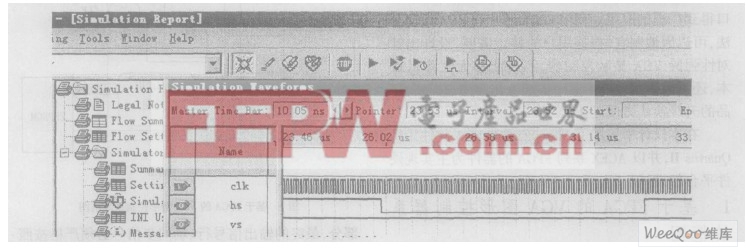

利用Altera 公司的QuartusII 軟件對(duì)VHDL 語言描述的VGA 時(shí)序控制模塊進(jìn)行編譯、仿真,可得到行同步信號(hào)HS , 場同步信號(hào)VS 的時(shí)序仿真波形,如圖3 所示。

圖3 時(shí)鐘信號(hào)仿真圖

由仿真結(jié)果波形可以看到,行同步信號(hào)的時(shí)鐘周期約為31. 9μs ,場同步信號(hào)的時(shí)鐘周期約為16。

6ms ,達(dá)到了VGA 標(biāo)準(zhǔn)時(shí)序的要求,可以為CRT 顯示器提供準(zhǔn)確的行場同步信號(hào)。

在硬件系統(tǒng)上,通過彩條圖案的生成驗(yàn)證了時(shí)序生成的正確性,可產(chǎn)生豎彩條、橫彩條、棋盤格等多種彩條模式。

評(píng)論