Virtex-5FPGA設計Gbps無線通信基站

3.2.2 多時鐘與亞穩態的解決

在通常的UART設計中,由于CPU時鐘與UART的數據接收、發送時鐘是處在不同的時鐘域,時鐘頻率和相位上存在差異,導致時序不能滿足建立時間和保持時間的要求,即數據的輸出處于不確定狀態,從而出現時序違反(slack0)和亞穩態。本文通過采用同步電路設計,有效地解決時序和亞穩態的問題[6][7]。

3.2.3 UART 核的綜合與優化

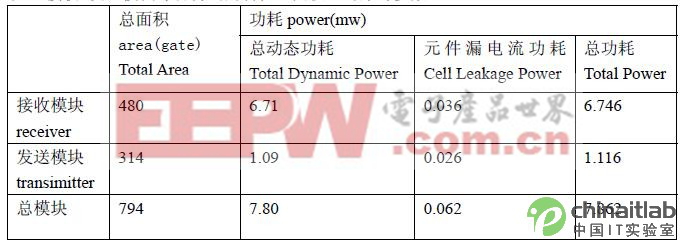

通過對RTL級進行優化,再仿真驗證正確后,可以對UART核進行綜合優化。本文采用SYNOPSYS軟件的design compile進行綜合優化,利用tcl(tool command language)語言編寫綜合優化的腳本。采用0.35um的工藝,將時鐘周期設置為5ns,在滿足時序(slack>0)的基礎上經過綜合優化,生成的時序、功耗、面積等參數如表1所示,優化后的功耗和面積滿足了ASIC/SoC的要求。

表1 接收/發送模塊綜合得出的功耗、面積、時序等參數

4 結束語

本文利用SYNOPSYS軟件設計IP核,更適合用于ASIC/SoC設計,而采用傳統的EDA軟件實現的則適合用在FPGA上,不適合用來做掩膜生成ASIC/SoC。本UART核的邏輯設計采用VerilogHDL語言,用狀態機和移位寄存器設計使整個設計的時序清晰,同時減少了接收模塊停止位的判斷,通過對RTL級優化避免了毛刺、亞穩態、多時鐘等問題,仿真和驗證采用的是SYNOPSYS軟件的VCS,通過對時序、功耗、面積的綜合考慮,最后通過SYNOPSYS軟件的design compile 綜合優化完成的IP 核可成功應用到ASIC/SoC 設計上。

本文作者創新點是利用SYNOPSYS軟件設計IP核,適合直接應用到ASIC/SoC設計中,并對RTL級做了優化,消除了在UART設計中碰到毛刺、亞穩態、多時鐘等問題;通過測試平臺(testbench)來仿真和驗證,RTL 代碼精簡,時序、面積和功耗都做了優化,達到了IP核的要求。

評論