Virtex-5FPGA設計Gbps無線通信基站

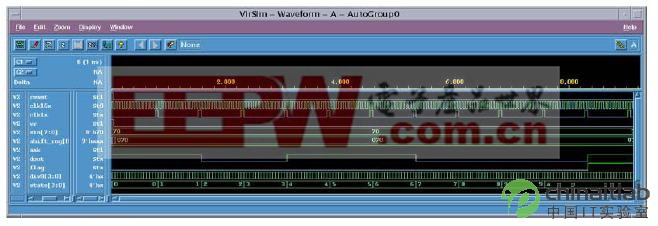

圖2 接收模塊的仿真波形

2.2.3 發送器模塊設計

發送器模塊將8位并行數據串行發出,用wr寫信號裝載并行進來的8位數據到9位移位寄存器(shift_reg)的低8位,最高位置為0,表示數據的起始位,數據發送完后發送1。

數據發送前先發送1表示等待數據的到來。等待16個clk16x之后,先發送一個1,再過16個clk16x之后,發送起始位0;以后每過16個clk16x,發送一位數據,直到數據發送完。16個clk16x用計數器設計,數據發送用狀態機實現。為了避免時序問題以及保證可測試性,采用單時鐘沿同步觸發,在15個clk16x到來時,將clk1x置1,在下一個clk16x時鐘的上升沿到來后發送一位數據,由于clk1x為高電平持續時間為一個clk16時鐘周期,也就是在clk1x的下降沿把一位數據發送出去。即

always@(posedge clk16x)

…………

if(clk1x==1)

…………

圖3給出發送模塊的仿真波形。由波形可以看出,當輸入的并行數據是70H,串行輸出正確,其中state、reset、clk1 x、flag和dout分別是狀態機、 復位信號、使異步的時鐘同步、數據發送出去的標志和串行數據輸出,而div8和ask分別是4位計數器和中斷請求信號。

圖3 發送模塊的仿真波形

3 UART 核的仿真、驗證與綜合、優化

3.1 UART 核的仿真和驗證

UART的功能仿真與驗證通過測試平臺(testbench)使用SYNOPSYS軟件的VCS工具,其流程如圖4所示[5]。接收和發送數據的正確性已通過圖2和3所示仿真波形驗證了。

圖4 基于testbench 的仿真流程

3.2 UART 核的綜合、優化

3.2.1 綜合存在的問題

一般在UART設計中,采用多時鐘,電平觸發,并且判斷數據的起始和停止采用額外的存儲器或計數器,這必然給驗證和綜合優化帶來時序上的問題,同時會產生毛刺和亞穩態,使得電路設計不夠完善。

3.2.2 毛刺的解決

在通常的UART設計中存在組合邏輯,當輸入的信號由高電平變低電平而其它某個信號由低電平變高電平時,由于在信號變化的瞬間,組合邏輯的輸出并非同時變化,而是有先后之分,將導致輸出出現尖脈沖,即產生毛刺。本文采用時鐘沿(上升沿)觸發,即將組合邏輯輸出端通過加到寄存器后輸出,從而避免毛刺的產生。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論