以智能型混合信號FPGA開發(fā)真正符合需求的系統(tǒng)

單芯片系統(tǒng)對嵌入式系統(tǒng)設計師來說,往往會隨著其面對的不同的系統(tǒng)設計而各有不同。例如,在龐大的娛樂或通信消費產(chǎn)品市場中,SoC意味著一顆具有數(shù)百萬邏輯門的集成電路(IC),其中包含許多大型定制邏輯模塊,并有將芯片的數(shù)字處理性能與外部世界連接的混合信號功能。在現(xiàn)實世界中,能夠支持這樣大規(guī)模的SoC開發(fā)的項目數(shù)量非常有限。

本文引用地址:http://www.czjhyjcfj.com/article/157459.htm

要實現(xiàn)能夠將所有重要功能集成在單一器件的設計理由很簡單,因為這樣就能將材料成本、部件庫存及電路板面積減至最低。另外,相較于多芯片解決方案,單芯片方案的功耗也較低,同時也有助于提高對知識產(chǎn)權的保護。如果一項設計功能的精髓能夠深植于單一芯片上,將會大大增加第三方取得這項設計的困難度。

單芯片夢想

對大部分的設計團隊來說,這樣的SoC目標仍然是一個夢想。能夠大量生產(chǎn)以支持一個完全定制化混合信號芯片開發(fā)的產(chǎn)品仍然是少數(shù)。絕大部分的產(chǎn)品都是采用專用標準產(chǎn)品(ASSP)或微控制器作為其解決方案的核心。在這樣的情況下,想要找到一個能夠完全符合項目需求的器件通常是一大難題。就定義來看,ASSP能夠為某一特定應用領域的設計問題提供一種解決方案,但是這樣的典型解決方案不可能完全符合真實世界中的項目需求。結果,通常是采用性能和參數(shù)超過需求的器件,或開發(fā)附加電路以彌補標準產(chǎn)品與實際需求之間的落差。此外,ASSP的靈活度不高,一旦選用了某顆IC,它的功能往往會限制產(chǎn)品后續(xù)的設計進展。

大部分的常用解決方案都不免會以微控制器(MCU)為基礎。雖然其軟件可編程性可提供不錯的靈活度,但是很少有MCU能提供與典型嵌入式設計需求完全相符的功能。大部分這類的設計都會在MCU之外另加入不同形式的可編程邏輯(FPGA或CPLD),以增加硬件中的邏輯功能。盡管現(xiàn)今市場上有各種帶有不同外設的MCU可供選用,但是絕大多數(shù)的嵌入式系統(tǒng)電路板上都沒有提供各種作為信號調(diào)節(jié)和I/O連接用途的模擬器件。

混合信號FPGA

愛特過去一直在通過提供Fusion混合信號FPGA,為上述設計提供解決方案。Fusion混合信號FPGA在單一器件上結合了高密度可編程邏輯和可配置模擬電路功能,另外還包括大容量的閃存模塊、完整的時鐘生成、管理電路以及在FPGA邏輯中嵌入微控制器軟核等設計選項。

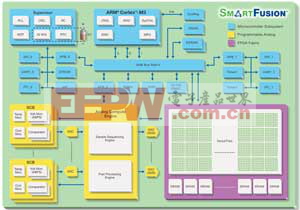

SmartFusion混合信號FPGA將高密度、基于閃存的FPGA、一個具完整外設組合的ARM Cortex -M3微控制器內(nèi)核,以及高效可編程模擬功能全部都集成在一顆單芯片上。

圖1 SmartFusion混合信號FPGA結構

ARM Cortex-M3處理器已不需要太多介紹。在SmartFusion芯片中,Cortex-M3處理器是個100MHz(125 DMIPS)器件,擁有最高容量為512KB的閃存和128KB的SRAM。在此系列FPGA中,處理器是一個硬核,這代表它是以最小面積來實現(xiàn)的,可帶來多項好處。它的效能足以執(zhí)行復雜算法,像精密電機控制、數(shù)個電機的多軸控制等。此外,在諸如系統(tǒng)管理等應用中,它能執(zhí)行所有的電壓監(jiān)測、排序、風扇控制,以及相關的系統(tǒng)基本運作,同時還具備充裕的能力來執(zhí)行更高級、用戶應用級別的任務。

外設與接口

與在SmartFusion器件中以更小面積實現(xiàn)處理器硬核的方式相同,此器件也包含了常用外設的完整組合。

圖2 SmartFusion系列器件具有豐富的外設及接口

SmartFusion器件提供一個10/100 Ethernet MAC(媒體存取控制器)和其他接口,諸如SPI、I2C以及UART。大量的數(shù)字(FPGA)I/O最快可執(zhí)行350MHz,并支持LVDS、PCI和LVPECL等I/O接口標準。慣于采用微控制器進行設計的工程師會喜歡此器件所包含的其他特性和功能,例如,實時時鐘、DMA控制器、外部存儲控制器、定時器和看門狗(watchdog)功能。

在硅片上,除了ARM Cortex-M3內(nèi)核,還有豐富的基于快閃的ProASIC 3 FPGA邏輯。此可編程邏輯可提供350MHz的系統(tǒng)效能;同時,SmartFusion系列器件最高可提供50萬門的可編程邏輯和108KB的內(nèi)建SRAM。基于快閃FPGA架構可完全免于由高能量輻射引發(fā)的固件錯誤(radiation-induced firm errors),此現(xiàn)象有時會影響基于SRAM的器件,同時也是許多嵌入式系統(tǒng)設計人員的主要考慮因素。由于FPGA的配置是設定在快閃單元(flash cell)中(ARM內(nèi)核可從片上閃存執(zhí)行),而整塊芯片是上電即用,無須等待配置文件從ROM或EPROM加載的時間。此外,閃存也能允許用來進行現(xiàn)場升級,但是有時出于系統(tǒng)安全考慮,這種現(xiàn)場升級功能被取消。在編程結束之后,進一步存取配置存儲器可被設置為永遠停用。

評論