基于MC8051軟核的星載智能1394終端

MC8051提供了參數化設計,通過修改VHDL中的參數值可以很輕易的修改內部模型,例如UART個數,Timer個數,選擇乘法器等。在本應用系統中不需要涉及乘除法運算,因此在配置文件mc8051_p.vhd中將常數C_IMPL_MUL, C_IMPL_DIV以及C_IMPL_DA的設置為0。

3.2.2時鐘和RAM設計

MC8051 IP核在Actel的APA600上綜合得到的最高時鐘頻率為15MHZ左右,為了使用于調試的串口波特率誤差最小,用Actel Libero內的SmartGen產生11.0592MHz的時鐘作為系統時鐘。

MC8051所需要的內部RAM和RAM都應該調用器件的底層單元來實現。以128字節的內部RAM為例。用SmartGen產生一個128*8大小的雙口RAM ram128_8.vhd,然后在mc8051_ram.vhd中例化。

3.2.3 ROM設計

MC8051完全兼容標準8051芯片,可采用KEIL uVision開發環境,建立工程文件時候Select Device選擇 Oregano Systems的8051 IP Core, 然后編譯寫好的51程序,產生HEX文件。需要從HEX文件中得到程序數據,這里簡單介紹一下HEX文件格式。HEX文件是由任意數量的十六進制記錄組成的,每個記錄包含5個域,他們以下面的格式排列[6]:

:llaaaatt[dd…]cc

HEX文件都是由冒號開頭的,ll是數據長度域,表示記錄中數據字節的個數;aaaa為地址域,標識記錄中數據字節的開始地址;tt是記錄類型域,51程序產生的hex文件只有兩種記錄類型,包括數據記錄(00)和文件結束記錄(01);dd是數據域,表示一個字節的數據

選用的Actel APA系列FPGA沒有底層的ROM單元,因此用VHDL設計實現ROM。通過了解了HEX文件的格式,編寫了從HEX文件讀取數據和地址信息,然后生成mc8051_rom.vhd文件,其中程序數據以常數的形式存在數組文件中。

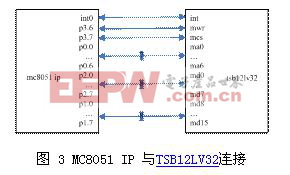

3.2.4 MC8051與TSB32LV32之間的接口

鏈路層芯片微處理器接口包括16位寬的數據總線以及7位寬的地址總線。可以通過設置鏈路層芯片的COLDFIRE,M8BIT_SIZ0,MCMODE_SIZE這三個端口的狀態,可以得到微處理器接口的各種不同操作模式,本設計中設置成16位MCS-MCA握手模式。

在系統頂層文件中對MC8051_top進行例化,連接MC8051與1394鏈路層芯片TSB12LV32。

MC8051的4組I/O口都是將輸入和輸出分開的,所以每組都可以配置成輸入和輸出。我們通過MCS和MWR來控制DM 和P1、P2口的連接。

MC8051通過TSB12LV32的微控制器接口實現對鏈路層和物理層內部寄存器的讀取和設置,其中對鏈路層芯片的寄存器讀寫直接通過微控制器接口操作,而對物理層芯片寄存器讀寫是通過對鏈路層24H的Phy Access Register讀寫實現。

1394芯片部分內部寄存器需要在系統上電的時候初始化或者在運行時候進行設置,一些則需要在運行時被監視以決定系統狀態,而鏈路層內部的異步發送FIFO和通用接收FIFO也是通過讀寫寄存器來訪問的。因此正確讀寫寄存器是1394接口實現中非常重要的一步。

通過正確設置控制寄存器,DM口控制器寄存器等內部寄存器便可以實現1394總線的各種傳輸模式的收發。

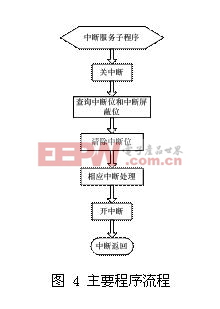

對1394芯片的控制另外一個主要部分是對中斷的響應和處理。將TSB12LV32芯片的INT管腳與MC8051的int0相連,通過int0的下跳沿檢測中斷發生。TSB12LV32芯片中有兩個寄存器是和中斷相關的。設置10H的中斷屏蔽寄存器中相應的某一位為1,則的0CH中斷寄存器響應位便跳變為高電平,同時產生相應的中斷。當有中斷發生的時候,INT管腳變低電平,而清除中斷則需要往中斷寄存器相應位寫入1。因此我們在中斷發生時候,可以通過讀取中斷寄存器的值查看發生了哪種中斷,然后做出正確的響應。

4 結論

我們根據本文介紹的方案,設計和研制了基于mc8051的1394總線接口。經過測試,1394總線系統工作正常。該總線接口具有集成度高,體積小,傳輸速率高等特點,同時可以根據實際任務需要很方便的擴充接口功能。本文介紹的方案對與1394總線接口的研究開發具有借鑒意義。

評論