基于Compact PCI體系的高性能監測測向處理平臺研究

就LTC2261來說,10 ps的時鐘抖動將在輸入頻率為1 MHz時產生0.8 dB的SNR損耗。而在輸入頻率為120 MHz時,SNR將被降低至41.1 dB。這給高精度時鐘電路設計帶來了挑戰,通常只有選擇昂貴的高性能壓控晶體振蕩器才能保證應有的性能。而美國國家半導體公司提供的超低噪聲時鐘抖動濾波器LMK04000系列提供了另外一種低成本的選擇。該濾波器采用簡潔的外置晶體及級聯PLLatinum架構,12 kHz~20 MHz的RMS抖動為150 fs,100 Hz~20 MHz抖動為200 fs,時鐘輸出信號為LVPECL/2VPECL、LVDS和LVCMOS,可以有效改善系統的性能及準確度。其特點是內置高性能的級聯鎖相環(共2個)、低噪聲晶體振蕩器、高性能的內置壓控振蕩器以及低噪聲分頻器和驅動器。第一個鎖相環有2個不同配置可供選擇,可以選用簡單的外置晶體振蕩器或壓控晶體振蕩器模塊執行濾除抖動功能。第二個鎖相環可利用內置壓控振蕩器產生低噪聲時鐘。

2.2 高速高流量數據存儲

采樣速率及分辨率越高,則轉換后的數據流傳輸帶寬越大,對后續數據傳輸的實時調度和連續存儲的要求就相應提高。現在通常采用的方法是通過擴展位寬以降低傳輸速率[4-6]。但是,如果通過擴展位寬實現高速數據流的實時海量數據存儲必將增大設備規模,對存儲深度或者持續采集時間的限制也是非常突出的。本文對存儲容量、訪問速度、存儲區管理的靈活性進行了研究,結合FLASH存儲陣列,設計實現了基于FLASH存儲器的高速高流量數據存儲卡。該存儲卡符合CPCI 6U標準,具有模塊化、標準化、易擴展以及高穩定性等特點,解決了數字后處理過程中在編碼分析和協議解析階段對連續無失真采樣數據的實時存儲難題。其主要研究內容包括:采用FPGA進行高速信號的調度處理和緩存,以解決高速數字接口的問題;采用超大規模FPGA實現對存儲區的可在線配置靈活管理,以實現整個模塊的高集成度、高可靠性、存儲區管理靈活(支持冗余備份)等目標。由此實現的海量數據存儲子系統結構采用標準化、模塊化設計,具有高速率、低功耗、可移植、易擴展的特性,可以滿足不同任務的需要。

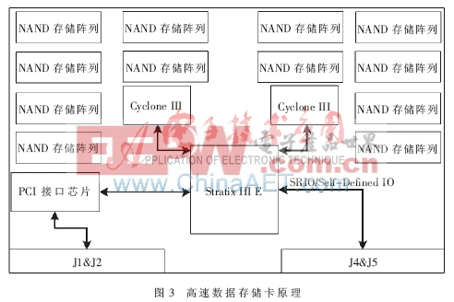

圖3所示是本文設計的基于CPCI標準的大存儲容量、高傳輸帶寬的通用數據存儲板。板載1片Stratix III E與2片Cyclone III FPGA以及96片NAND FLASH。StratixIII E是存儲板數據接收和分發的樞紐,該器件可應對存儲器較多的應用,為采用乒乓結構對數據進行緩存提供資源,主要完成以下功能:提供高達1 Gb/s的差分傳輸速率;通過PCI接口芯片PCI9656連接到PCI總線上,實現64 bit的局部總線;通過J4/J5實現板間自定義的高速差分數據傳輸。2片低成本Cyclone III分別連接48片NAND,實現數據的高速分發和NAND陣列的二級管理。在高速數據存儲卡的設計過程中,打通主機與存儲模塊之間的數據傳輸通道是調試的重點,這涉及FPGA中PCI本地端匹配邏輯的設計。一個典型的基于狀態機設計的匹配邏輯時序如圖4所示。本文引用地址:http://www.czjhyjcfj.com/article/151775.htm

評論