短幀Turbo譯碼器的FPGA實現

Turbo碼雖然具有優異的譯碼性能,但是由于其譯碼復雜度高,譯碼延時大等問題,嚴重制約了Turbo碼在高速通信系統中的應用。因此,如何設計一個簡單有效的譯碼器是目前Turbo碼實用化研究的重點。本文主要介紹了短幀Turbo譯碼器的FPGA實現,并對相關參數和譯碼結構進行了描述。

本文引用地址:http://www.czjhyjcfj.com/article/151302.htm1 幾種譯碼算法比較

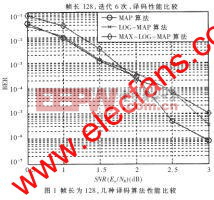

Turbo碼常見的幾種譯碼算法中,MAP算法[1][3]具有最優的譯碼性能。但因其運算過程中有較多的乘法和指數運算,硬件實現很困難。簡化的MAP譯碼算法是LOG-MAP算法和MAX-LOG-MAP算法,它們將大量的乘法和指數運算轉化成了加減、比較運算,大幅度降低了譯碼的復雜度,便于硬件實現。簡化算法中,LOG-MAP算法性能最接近MAP算法,MAX-LOG-MAP算法次之,但由于LOG-MAP算法后面的修正項需要一個查找表,增加了存儲器的使用。所以,大多數硬件實現時,在滿足系統性能要求的情況下,MAX-LOG-MAP算法是硬件實現的首選。通過仿真發現,采用3GPP的編碼和交織方案[2],在短幀情況下,MAX-LOG-MAP算法同樣具有較好的譯碼性能。

如圖1所示,幀長為128,迭代6次,BER=10-5的數量級時, MAX-LOG-MAP算法的譯碼性能比MAP算法差大約0.6dB,比LOG-MAP算法差0.2dB左右。所以,本文采用3GPP的交織和(13,15)編碼方案,MAX-LOG-MAP譯碼算法進行短幀Turbo碼譯碼器的FPGA實現與設計。

2 MAX-LOG-MAP算法

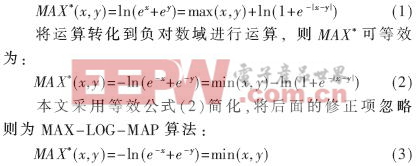

為對MAP算法進行簡化,通常將運算轉換到對數域上進行,避免了MAP算法中的指數運算,同時,乘法運算變成了加法運算,而加法運算用雅可比公式簡化成MAX*運算[4]。

將運算轉化到正對數域進行運算,則MAX*可等效為:

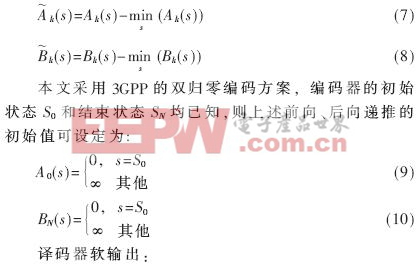

按照簡化公式(3)對MAP譯碼算法[1][3]的分支轉移度量、前向遞推項、后向遞推項及譯碼軟輸出進行簡化。

分支轉移度量:

為防止迭代過程中數據溢出,對前后向遞推項(5)、(6)式進行歸一化處理:

評論