針對FPGA的完全可配置嵌入式32位RISC處理器

Mico32可以用于各種存儲系統,同時使用內嵌存儲器用于存儲指令和數據。內嵌存儲器可以建立一個本地哈佛結構,并允許單周期訪問指令和數據。對于更大的存儲器需求,處理器通過一個仲裁器連接到其他的存儲器模塊或接口。這可以是用FPGA的存儲器資源來實現的 “片上”存儲器,或接口至外部存儲器,諸如SSRAM、Flash和DRAM。處理所有訪問協議至外部存儲器的合適接口模塊是由MSB提供的。提供可選的指令和數據高速緩存,能夠配置成各種選擇(高速緩存的大小,高速緩存塊的大小等等)。

通過一個開放源碼Wishbone總線接口,該處理器連接到各種外圍元件。針對快速周轉周期,圖形用戶界面可以輕松和快速地創建處理器平臺。除了標準存儲器控制器,這可能包括各種接口,不僅支持I2C、通用IO、定時器,UART以及SPI,還能支持更復雜的模塊,如PCI接口或TriSpeed以太網MAC。

直接存儲器訪問(DMA)控制器是可用的,添加主器件(master)至Wishbone總線,以免除處理器的數據傳輸工作。這也允許有DMA功能的外設高效地直接傳輸數據到存儲系統,從而節省了片上總線的帶寬。

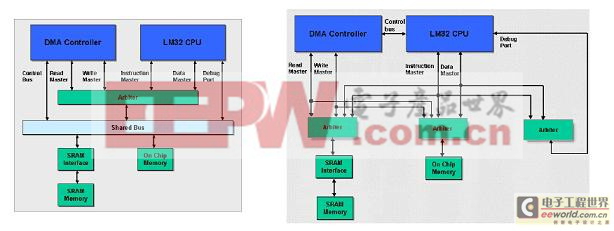

除了外圍元件和DMA,用戶可以自定義仲裁方案。總線結構產生器支持主器件(master)方和從器件(Slave)方的總線仲裁。如果能夠滿足系統性能的要求,主器件方總線仲裁提供了一個簡單的低成本解決方案。然而,如果在設計中有多個總線主器件和多個從器件,在任何時間主器件方總線仲裁限制與單總線主器件通信。在許多設計中,通過兩個或兩個以上的總線主器件同時與獨立的從器件進行通信,從器件方仲裁改進了性能。圖3展示了可用的仲裁方案。

圖3 仲裁方案

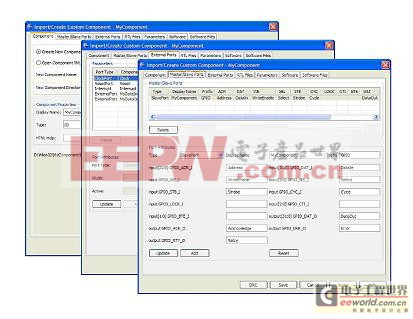

用戶還可以創建自己的基于Wishbone總線的外設元件,然后通過整合到MSB自動連接到總線。因此,LatticeMico32的架構提供了兩種可能性:第一,人們可以創建定制的元件,將它放人MSB中的可用元件列表(圖4)。第二,可以構建出所謂的Passthru元件,可以將Wishbone接口引出到核的外面,因此,用戶可以在FPGA的其他部分添加任何邏輯塊。

圖4 創建定制的外圍組件

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論