基于Matlab/DSP Builder任意波形信號發生器的兩種設計

0 引言

在當今的科技信息社會中,尤其是在電子設計和信號測試系統中,通常需要一些復雜、特定頻率的信號,通常的信號發生器難以滿足要求,市場上出售的一些任意信號發生器的價格昂貴,體積較大,不能滿足實際的需要。

Altera DSP Builder是一款系統級的設計工具,依賴于Mathworks公司的數學分析工具Matlab/Simulink,可以在Sireulink中進行圖形化設計和仿真,同時又可以通過signalCompiler把Matlab/Simulink的模型文件(.mdl)轉換成相應的硬件描述語言VHDL,本文用兩種方法,即傳統型的任意信號發生器和基于直接數字頻率合成(DDS)的任意信號發生器,在DSPBuilder的開發工具下實現任意信號發生器的設計,不涉及到編程,操作簡單。

1 傳統型任意信號發生器的設計

1.1 設計原理

傳統型任意信號發生器原理比較簡單,將時鐘源作為地址發生器(計數器)的輸入時鐘,通過改變時鐘源的頻率,可以實現調整地址發生器(計數器)產生地址的變化速率,從而達到改變輸出波形與輸出頻率的目的。當地址發生器輸出值等于待生成波形數據存儲器中波形數據的地址時,待生成波形數據存儲器將輸出此數據到高速D/A轉換,將其變為模擬信號,經低通濾波器后輸出所需波形。D/A的輸出頻率fuot與待生成波形數據存儲器的波形數據點數N以及時鐘源的頻率fclk關系為:

![]()

由式(1)可知,只要改變數據波形點數N就能控制輸出信號的頻率。

1.2 系統設計

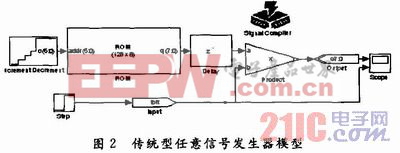

根據圖1所示的原理框圖,在Matlab/DSP Builder平臺上,建立傳統型任意信號發生器的Simulink模型,如圖2所示。

在圖2中,Increment Decrement模塊起到一個地址發生器的作用,隨著時鐘的輸入不斷累加輸出,ROM模塊存放待生成信號的波形數據,輸入模塊input通過produt模塊控制信號的輸出。

利用Matlab強大的仿真功能,方便、快捷地生成給定頻率、周期、脈寬的任意波形數據,但生成的數據通常是浮點型的,要將其轉換為十六進制的Hexadecimal(Itel-Form)File(.hex)格式的文件,然后將*.hex文件添加到ROM存儲器中,設置系統模型的參數,就可以得到任意信號波形。

2 基于DDS的任意信號發生器的設計

2.1 設計原理

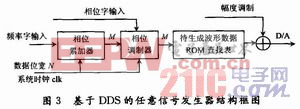

基于DDS的任意信號發生器結構框圖如圖3所示。由圖3可以看出,相位累加器在系統時鐘的控制下以頻率控制字長的步長進行累加,輸出的線性相位序列和相位控制字相加后對待生成波形數據ROM查表尋址,待生成波形數據ROM查找表輸出相應波形的離散序列,再由DAC將其轉換為模擬量,把存入的數據重新整合起來。此過程實際完成了相位到幅度的轉換。

設系統時鐘為fclk,頻率輸入字為Freword,相位輸入字為Phaseword,N是相位累加器的數據位寬(頻率輸入字的數據位寬),相位調制器的位寬為M,則DDS的輸出信號頻率為:

![]()

輸出信號的相移為:

![]()

由式(2)和式(3)可知,改變頻率輸入字和相位輸入字就可以分別控制輸出信號的頻率和相位。

評論