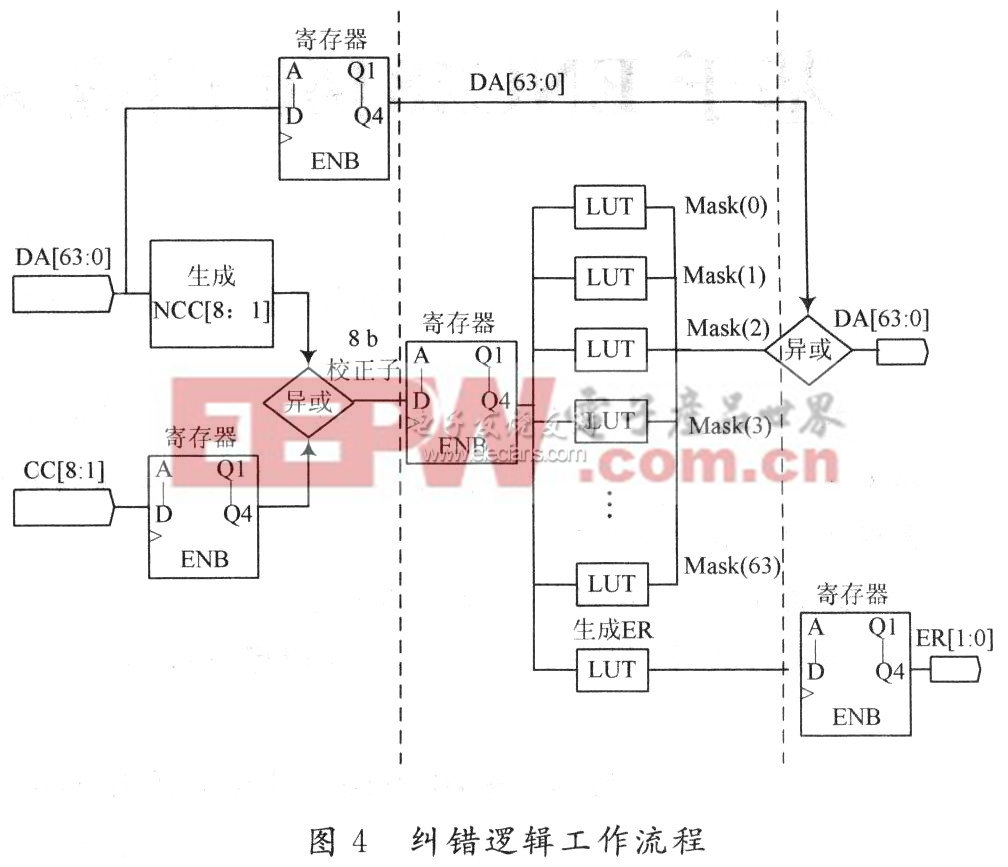

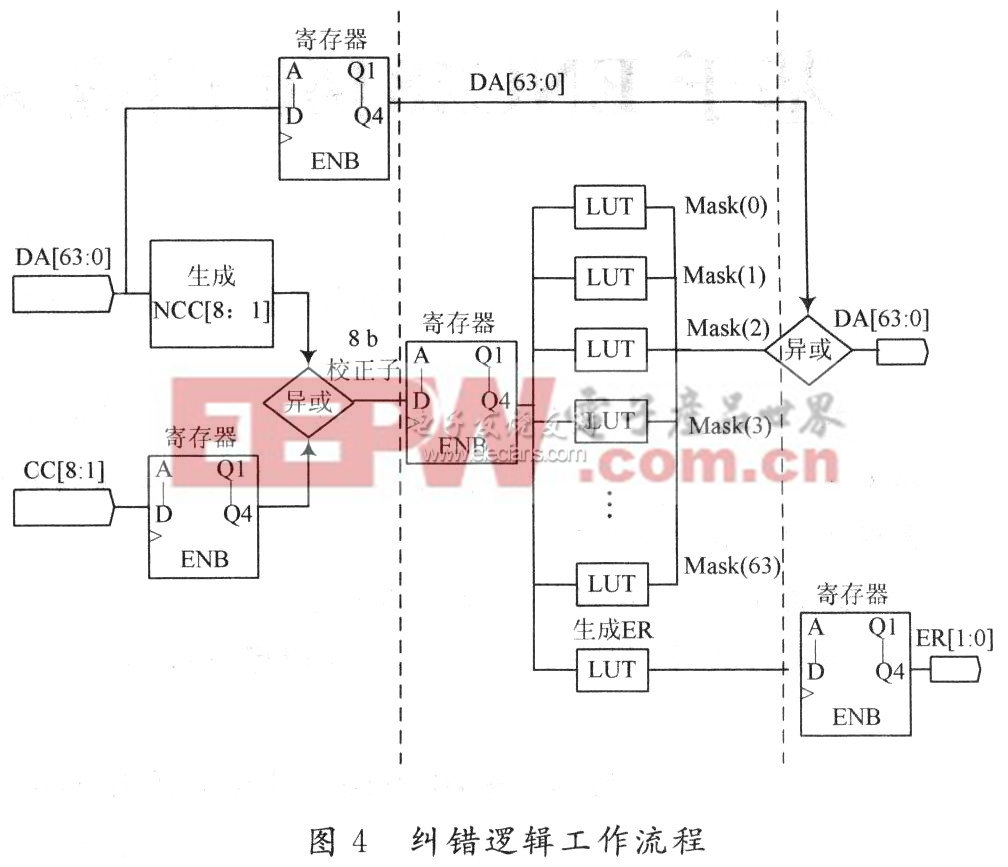

基于FPGA的檢糾錯邏輯算法的實現(xiàn)

3 結(jié) 語

對綜合后進行仿真的結(jié)果進行分析,期間人為地加入1位、2位、3位隨機分布的數(shù)據(jù)位錯誤,該系統(tǒng)能夠在2個系統(tǒng)時鐘周期內(nèi)對1位錯誤的情況成功地檢測并予以糾正;對2位和3位錯誤情況也都進行了正確的類別判定。仿真結(jié)果表明,設(shè)計的系統(tǒng)比較理想,能滿足設(shè)計要求。

EEPW首頁 > 嵌入式系統(tǒng) > 設(shè)計應(yīng)用 > 基于FPGA的檢糾錯邏輯算法的實現(xiàn)

3 結(jié) 語

對綜合后進行仿真的結(jié)果進行分析,期間人為地加入1位、2位、3位隨機分布的數(shù)據(jù)位錯誤,該系統(tǒng)能夠在2個系統(tǒng)時鐘周期內(nèi)對1位錯誤的情況成功地檢測并予以糾正;對2位和3位錯誤情況也都進行了正確的類別判定。仿真結(jié)果表明,設(shè)計的系統(tǒng)比較理想,能滿足設(shè)計要求。

評論