采用CPLD的專用鍵盤接口芯片的方案設計

鍵盤掃描時序的基本原理[4]可以用圖3所示的狀態圖表示。狀態圖的輸入變量為RST(復位)、KEY-PRESS(有按鍵)、TIMER-OVER(去抖動延時結束);輸出變量包括EN-SCAN(掃描行轉移)、EN-CODED(鍵盤編碼啟動)、START-TIMER(開啟去抖動延時)。從圖3中知道,狀態S0→S1→S2為按鍵掃描狀態鏈,狀態S3→S4→S5為去抖延時狀態鏈,狀態S6為按鍵保持期。當按鍵被按下時,進入啟動(S3)去抖延時狀態鏈;去抖延時結束后(S5),若按鍵沒有按下則恢復掃描狀態鏈(S0);若按鍵確認被按下則進入保持期(S6),并輸出按鍵編碼維持至按鍵松開。

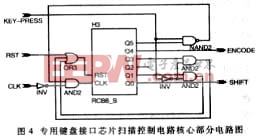

根據狀態圖3和上述的狀態轉移描述,進行鍵盤掃描控制電路的設計,結果如圖4所示。其中H3是6位循環移位寄存器,由時鐘CLK觸發實現狀態移位。移位寄存器的輸出Q0~Q5分別代表鍵盤掃描控制電路的狀態S0~S6,當然它們并非一一對應,但實現的功能相同。值得一提的是,如果專用鍵盤芯片KB-CORE的外部時鐘CLK來自單片機的ALE信號(如圖1所示),當單片機時鐘為6MHz時,則專用鍵盤芯片KB-CORE的外接時鐘為1MHz的方波信號,信號周期為1μs。如果將該時鐘信號經過一個分頻器,使其輸出的信號周期約為Tclk=1μs×212≈4ms,然后再作為H3的時鐘信號。這意味著鍵盤掃描控制電路約4ms掃描一行按鍵。如果H3中的Q2態沒有被使用,則可以實現約8ms的去抖動延時。通過這樣的設計,可以免除延時計數器,簡化電路。

本文引用地址:http://www.czjhyjcfj.com/article/149206.htm

4 專用鍵盤接口芯片的實現

根據實時數據校正系統的設計要求,使用了34個自定義I/O引腳和PC44封裝的CPLD來實現專用鍵盤接口芯片KB-CORE。芯片型號的選擇依據綜合所需要的宏單元(Macrocells)個數決定。如果借助硬件描述語言VHDL[5]對上述設計進行描述,綜合結果需要約140個宏單元;如果改用原理圖輸入方式,則只需約60個宏單元。因此選用XC9572芯片可以滿足上述專用鍵盤接口芯片KB-CORE的要求。實際使用如圖1和圖2所示,操作結果表明鍵盤接口芯片性能穩定。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論