高速DSP系統的電路板級電磁兼容性分析與設計

隨著高速DSP技術的廣泛應用,相應的高速DSP的PCB設計就顯得十分重要。由于DSP是一個相當復雜、種類繁多并有許多分系統的數、模混合系統,所以來自外部的電磁輻射以及內部元器件之間、分系統之間和各傳輸通道間的串擾對DSP及其數據信息所產生的干擾,已嚴重地威脅著其工作的穩定性、可靠性和安全性。據統計,干擾引起的DSP事故占其總事故的90%左右。因此設計一個穩定、可靠的DSP系統,電磁兼容和抗干擾至關重要。

本文引用地址:http://www.czjhyjcfj.com/article/148519.htm1 DSP的電磁干擾環境

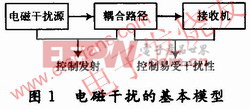

電磁干擾的基本模型由電磁干擾源、耦合路徑和接收機3部分組成,如圖1所示。

電磁干擾源包含微處理器、微控制器、靜電放電、瞬時功率執行元件等。隨著大量高速半導體器件的應用,其邊沿跳變速率非常快,這種電路可以產生高達300 MHz的諧波干擾。耦合路徑可以分為空間輻射電磁波和導線傳導的電壓與電流。噪聲被耦合到電路中的最簡單方式是通過導體的傳遞,例如,有一條導線在一個有噪聲的環境中經過,這條導線通過感應接收這個噪聲并且將其傳遞到電路的其他部分,所有的電子電路都可以接收傳送的電磁干擾。例如,在數字電路中,臨界信號最容易受到電磁干擾的影響;模擬的低級放大器、控制電路和電源調整電路也容易受到噪聲的影響。

良好的電路板布線在電磁兼容性中是一個非常重要的因素,一個拙劣的電路板布線和設計會產生很多電磁兼容問題,即使加上濾波器和其他元器件也不能解決這些問題。

正確的電路布線和設計應該達到如下3點要求:

(1)電路板上的各部分電路之間存在干擾,電路仍能正常工作;

(2)電路板對外的傳導發射和輻射發射盡可能低,達到有關標準要求;

(3)外部的傳導干擾和輻射干擾對電路板上的電路沒有影響。

2.1 元器件的布置

(1)元器件布置的首要問題是對元器件進行分組。元器件的分組原則有:按電壓不同分;按數字電路和模擬電路分;按高速和低速信號分和按電流大小分。一般情況下都按照電壓不同分或按數字電路與模擬電路分。

(2)所有的連接器都放在電路板的一側,盡量避免從兩側引出電纜。

(3)避免讓高速信號線靠近連接器。

(4)在元器件安排時應考慮盡可能縮短高速信號線,如時鐘線、數據線和地址線等。

2.2 地線和電源線的布置

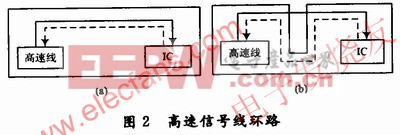

地線布置的最終目的是為了最小化接地阻抗,以此減小從電路返回到電源之間的接地回路電勢,即減小電路從源端到目的端線路和地層形成的環路面積。通常增加環路面積是由于地層隔縫引起的。如果地層上有縫隙,高速信號線的回流線就被迫要繞過隔縫,從而增大了高頻環路的面積,如圖2所示。

圖2中高速線與芯片之間進行信號傳輸。圖2(a)中沒有地層隔縫,根據“電流總是走阻抗最小的途徑”,此時環路面積最小。圖2(b)中,有地層隔縫,此時地環路面積增大,這樣就產生如下后果:

(1)增大向空間的輻射干擾,同時易受空間磁場的影響;

(2)加大與板上其他電路產生磁場耦合的可能性;

(3)由于環路電感加大,通過高速線輸出的信號容易產生振蕩;

評論