KCPSM6 PicoBlaze的原理與應用

引言

PicoBlaze 8位嵌入式處理器是Xilinx公司為Virtex、Spartan系列FPGA和CoolRunner—II系列CPLD設計的嵌入式處理器軟核。針對不同的器件,Xilinx公司共推出了3個版本的PicoBlaze,包括KCPSM3(目標器件為Spartan 3、Virtex II、Virtex II PRO、Virtex 4和Virtex 5)CPLD版(目標器件為CoolRunner—II)和最新推出的KCPSM6(目標器件為Spartan 6、Virtex 6和7系列FPGA)。KCPSM6針對Spartan 6、Virtex 6和7系列FPGA進行了特殊優化,增加了一些新特性,在開發和調試方法上也與KCPSM3有所不同。本文分析對比了其異同,對KCPSM6在開發調試中的注意事項進行總結,并在Avnet Spartan 6 MicroBoard上進行了實例驗證。

1 KCPSM6 PicoBlaze的體系結構

KCPSM6 PicoBlaze(以下簡稱KCPSM6)8位嵌入式處理器是Xilinx公司為Spartan 6、Virtex 6和7系列FPGA設計的嵌入式處理器軟核,它具有效率高、占用資源少等優點,可以方便地嵌入到硬件系統設計中,實現與其他功能模塊的無縫連接。它僅占用26個Slice和1個BRAM,占XC6SLX4器件4.3%的資源、XC6SLX150T器件不到0.11%的資源。KCPSM6嵌入式處理器具有高達52~120 MIPS的指令執行速度,具體速度取決于所選用的FPGA所屬系列和器件速度等級。

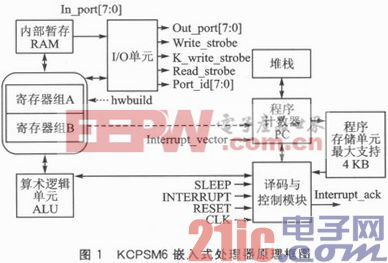

KCPSM6微處理器主要由以下幾個單元組成:

◆兩組16個8位通用寄存器;

◆最高支持4 KB的程序存儲單元;

◆8位算術邏輯單元,帶有CARRY和ZERO標志位;

◆64、128或256字節內部暫存RAM;

◆256個輸入和256個輸出端口,方便擴展應用;

◆中斷控制單元;

◆休眠模式,進一步降低系統功耗。

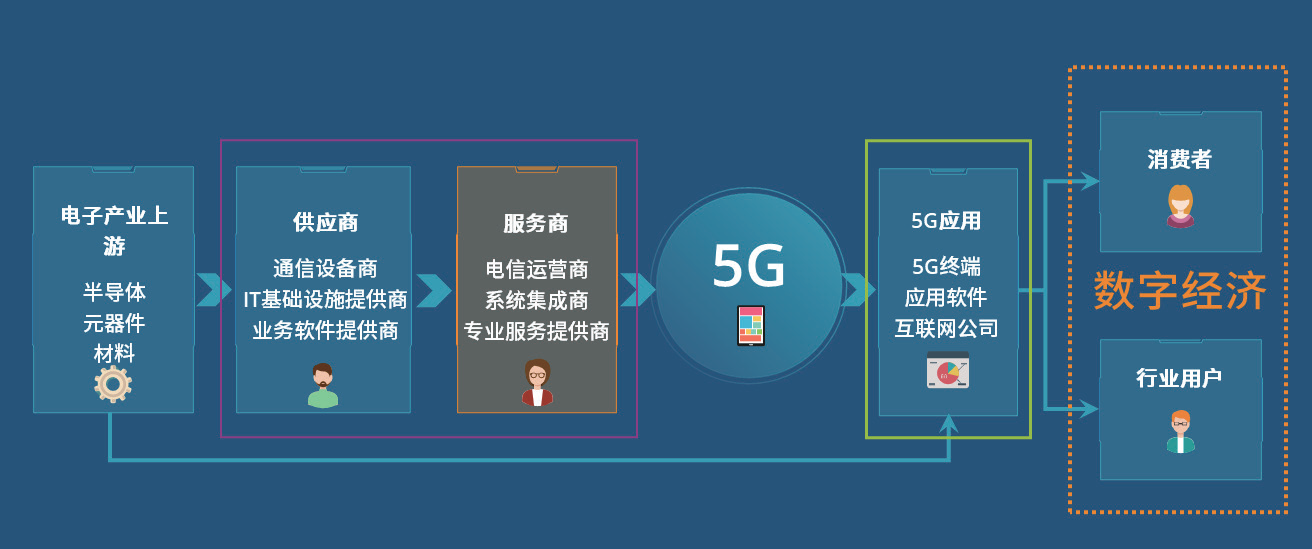

KCPSM6嵌入式處理器的原理框圖如圖1所示。

KCPSM6新增的特性和功能總結如下:

(1)新增引腳

sleep引腳。當sleep引腳電平由低變高時,KCPSM6在執行完最后一條已讀取指令后,進入休眠模式,以降低系統功耗。若將sleep引腳一直置低電平,則KCPSM6一直處于正常工作狀態。

K_write_strobe為常量輸出觸發信號,與OUTPUTK指令配合使用,可用一條指令即可完成向輸出端口輸出常量值,而無需寄存器的干預。

bram_enable為程序存儲單元BRAM使能信號,可進一步降低系統功耗。

Address[11:10]為程序存儲單元高位地址線,最大支持4 KB程序存儲。

評論