三模冗余乘法器的設計與實現

前言

本文引用地址:http://www.czjhyjcfj.com/article/128750.htm現場可編程門陣列(Field Programmable Gate Array,FPGA)可通過用戶軟件編程來配置生成硬件電路,極大提高了電子系統設計中的靈活性和通用性,因而被廣泛應用于航天、通信、醫療和工控等重要領域。但在空間環境中,基于SRAM的FPGA容易受SEU(Single Event Upset)和SETs(Single Event Transients)的影響,從而導致系統故障。DMR(Dual Modular Redundancy)和TMR(Triple Modular Redundancy)是系統冗余設計的有效手段,本文設計了一個基于FPGA的三模冗余乘法器。

系統總體方案

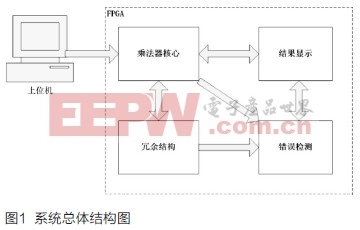

本系統采用Xilinx公司的Spartan-6 XC6SLX45 FPGA作為系統開發平臺,在含有Windows XP操作系統和集成開發環境Xilinx ISE 13.2的PC作為系統的開發環境,開發了一種基于三模冗余的乘法器運算核心冗余系統,系統的結構如圖1。

強大的系統開發環境:系統開發環境為含有Windows XP操作系統和集成開發環境Xilinx ISE 13.2的PC機作為系統開發環境。Xilinx ISE系統功能有:1.提供了Verilog語法顏色顯示功能,程序很容易查錯;2.自行生成程序框架,可以加快系統開發速度縮短系統開發周期;3.多軟件協同綜合和仿真,ISE內部可以使用集成的仿真功能組件ISIM和網表綜合功能組件XST,也可以指定其它公司的仿真和綜合工具作為ISE環境的默認開發工具;4.底層布局布線編輯和時序、面積和I/O約束,系統可對生成的布局布線后網表進行自行修改其布局布線情況,以進一步來增強系統性能,通過對系統各種關鍵路徑進行時序約束可以增加系統運行頻率,對模塊進行面積約束可以減少系統FPGA資源消耗。

評論