MIPS -- 適用于MCU的處理器

5.低功耗與緊湊設計

本文引用地址:http://www.czjhyjcfj.com/article/118393.htm典型SoC的大部分功耗和面積來自于處理器內核外部的存儲器、外設和控制邏輯。然而MIPS科技明白,在單片機設計中,除了最佳的性能效率外,芯片成本和功耗也是產品取得成功的關鍵因素。MIPS在處理器內核設計中加入了特定功能,以最大程度地減少面積和功耗,本節將介紹其中一些功能。MIPS科技通過提供最佳的面積和功耗解決方案鞏固了其在性能上的領先地位,具體內容將通過以下幾節中M4K與Cortex-M3的比較結果為您展示。

5.1 低功耗特性

M4K微架構的高性能允許應用工作于比其他內核更低的時鐘頻率。功耗與頻率成正比,因此降低頻率就是降低功耗。如前文所述,M4K內核的處理性能至少比Cortex-M3高20%,即功率效率(DMIPS/mw)更為出色,這意味著完成同一項作業需要的功耗更低。M4K內核的高性能有助于降低功耗,因為它可以更快地完成任務,從而有更多時間處于低功耗(空閑)狀態下。

M4K內核是可綜合設計,在不同低功耗工藝和物理庫之間可任意移植。該內核是靜態設計,允許時鐘實時變化(需要時降至較低頻率)。它甚至支持時鐘停止,這會將功耗降至最低的uW級別(這種情況下的功耗主要取決于工藝上的漏電流)。

M4K內核提供多種功耗管理功能,通過使用微調時鐘門控來控制動態功耗并支持掉電模式。M4K內核的大部分功耗來自于時鐘邏輯和寄存器。在整個M4K內核中大量采用時鐘門控,這可以提供一種有效的機制,即對于內核中的選定區域,當不使用時可將其關閉。M4K內核還提供一種機制,即使用內部寄存器通過特定WAIT指令控制內核進入低功耗和休眠模式。當執行WAIT指令時,內部時鐘暫停,流水線凍結。任何中斷或復位都將使內核退出休眠模式并恢復正常工作。

這些有效的功耗管理功能,連同低功耗設計工具的支持,都有助于顯著降低動態功耗。與來自ARM網站的數據相比,在相似的配置和頻率下,我們發現在采用180 nm制程時,M4K內核與Cortex-M3的動態功耗(mW/MHz)相似。

但采用90 nm制程時,工作在50 MHz且經面積優化的Cortex-M3的功耗為0.10 mW/MHz,額定功效為12.5(DMIPS/mW)。在相同的90 nm節點以及更高的200 MHz時鐘頻率和經面積優化的配置下,M4K的功耗僅為0.04 mW/MHz:與Cortex-M3相比,功耗降低60%,而功效是其2倍。

M4K內核在130 nm制程時顯示出相似的低功耗特性。由于沒有Cortex-M3在130 nm制程下的數據可供比較,因此下面我們只給出M4K在130 nm制程下的功耗數據:

在最大頻率216 MHz以及經速度優化的配置下,功耗為0.17 mW/MHz

在100 MHz頻率以及經面積優化的配置下,功耗為0.06 mW/MHz

5.2 小尺寸特性

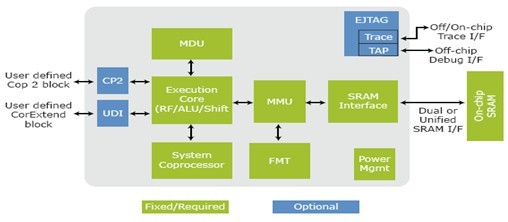

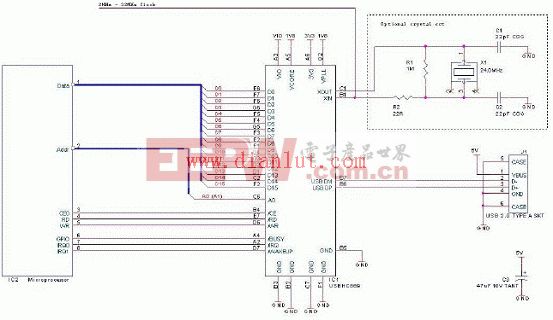

M4K內核是高效、高度可配置且靈活的處理器內核。圖5顯示了M4K內核中的可選模塊,包括調試/跟蹤(ETAG)、CP2協處理器接口和CorExtend擴展。MIPS16e ASE指令解碼器是可選的。

圖5:M4K內核框圖

為減少門數規模,M4K內核提供了一組全面的配置選項。可配置選項包括使能/禁止調試功能、設置調試/跟蹤斷點的數量和類型、快速或慢速MDU、設置GPR寄存器的數量以及統一或合并數據和地址SRAM接口統一或分離。

這些配置選項綜合用于實現速度或面積優化,以滿足所需的應用目標頻率,同時生成最小尺寸和最低門數。內核面積取決于工藝、單元庫和目標性能。要對M4K與Cortex-M3在內核面積方面進行有意義的比較,應該考慮到這些因素。不過M4K內核的門數可低至33K,那么即便不考慮其功能多于Cortex-M3,M4K內核的尺寸仍比Cortex-M3小。

6.生態系統

SoC開發環境(包括硬件/軟件調試工具和其他第三方解決方案)是處理器選型中的重要考慮因素。

MIPS科技擁有一個專門團隊,提供一系列硬件和軟件開發工具,幫助設計人員在SoC中成功集成和測試MIPS處理器內核,并在目標系統應用中驗證其工作情況。這些工具包括System Navigator™ EJTAG仿真器、支持RTOS和Linux系統的GNU軟件工具鏈、用于軟件評估和協同模擬的周期精確與指令精確的模擬器、基于FPGA的開發/評估板和Navigator集成開發環境元件套件(ICS),以及基于Eclipse且與其他MIPS工具完全整合的開發環境。

圖6:System Navigator調試探針和SEAD3開發板

此外,MIPS科技還建立了MIPS聯盟計劃(MAP),以支持其廣泛的第三方生態系統。MAP是一個由100多個合作伙伴組成的群體,提供了數百種支持MIPS架構和處理器內核的解決方案。對于那些想通過MIPS兼容工具縮短上市時間的設計人員以及以各種市場應用(包括MCU)為目標的解決方案來說,該生態系統是一個很好的資源。

評論