基于CPLD內(nèi)部的反向器實(shí)現(xiàn)振蕩器應(yīng)用

摘要:使用CPLD內(nèi)部的資源施密特觸發(fā)器和反相器,只需外加一個(gè)RC就可以設(shè)計(jì)出一個(gè)穩(wěn)定的振蕩器,為CPLD或外圍器件提供時(shí)鐘源。靈活方便的設(shè)計(jì)及低成本的特性,使之具有很好的產(chǎn)品商業(yè)使用價(jià)值。

本文引用地址:http://www.czjhyjcfj.com/article/113013.htm關(guān)鍵字:CPLD;施密特觸發(fā)器;振蕩器

前言

電子技術(shù)的飛速發(fā)展,尤其是消費(fèi)類(lèi)電子產(chǎn)品在成本、產(chǎn)品功能及品質(zhì)的更高要求,使消費(fèi)類(lèi)電子產(chǎn)品的設(shè)計(jì)不是簡(jiǎn)單地要求設(shè)計(jì)出來(lái),而是要考慮低成本高品質(zhì)。 CPLD的成本低,占用PCB面積小,功耗低和靈活的后期可編程特性在嵌入式設(shè)計(jì)中得到越來(lái)越廣泛的應(yīng)用。

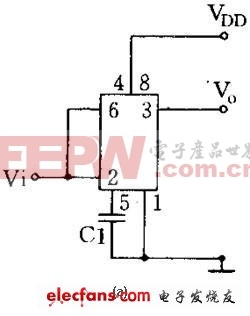

由于CPLD資源較小,大部分工程師都用CPLD來(lái)實(shí)現(xiàn)整合邏輯電路,擴(kuò)展主處理器的I/O功能,或做電源管理功能,由于CPLD內(nèi)部沒(méi)有振蕩器,而振蕩器的功能對(duì)于CPLD做電源管理,產(chǎn)品的系統(tǒng)管理尤為重要,如果在CPLD外部加一個(gè)振蕩器就增加了整個(gè)設(shè)計(jì)的成本。利用CPLD內(nèi)部的反向器,再加上外部簡(jiǎn)單的RC,即可以實(shí)現(xiàn)一個(gè)簡(jiǎn)單的振蕩器供CPLD內(nèi)部設(shè)計(jì)使用,可以降低設(shè)計(jì)成本,靈活性強(qiáng),穩(wěn)定性高。

CPLD內(nèi)部施密特觸發(fā)器

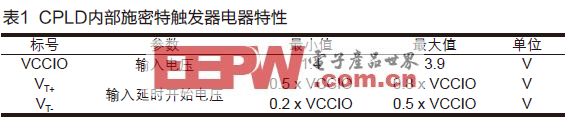

CPLD內(nèi)部施密特觸發(fā)器電器特性見(jiàn)表1。目前大部分使用的CPLD都需要兩個(gè)電源VCC和VCCIO,VCC就是CPLD內(nèi)部的核電壓,VCCIO是CPLD所有I/O 引腳電壓。

從表1看出,VT+和VT-是取決于VCCIO的電壓。目前大部分設(shè)計(jì)都選用VCCIO為3.3V,所以,VT+ (min.) = 0.5 × 3.3V = 1.65V,VT+ (max.) = 0.8× 3.3V = 2.64V

VT- (min.) = 0.2 × 3.3V = 0.66V VT-(max.) = 0.5 × 3.3V = 1.65V

從上面給出的VCCIO 為3.3V計(jì)算可以看出,對(duì)于施密特觸發(fā)器當(dāng)輸入電壓在1.65V下輸出都為低電平,當(dāng)輸入電壓在1.65V之上都為高電平,1.65V為高低電平的臨界點(diǎn)。

評(píng)論