刻蝕工藝流程及設備市場份額

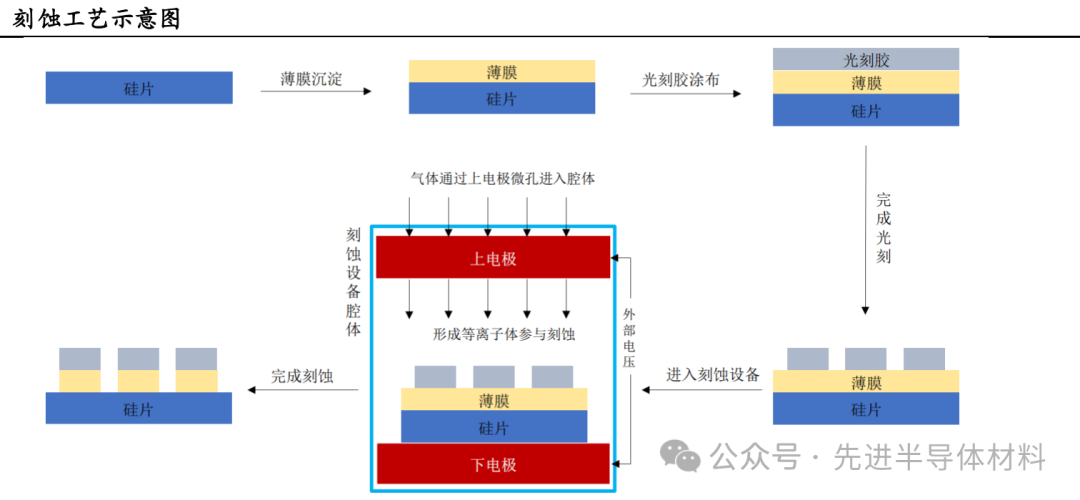

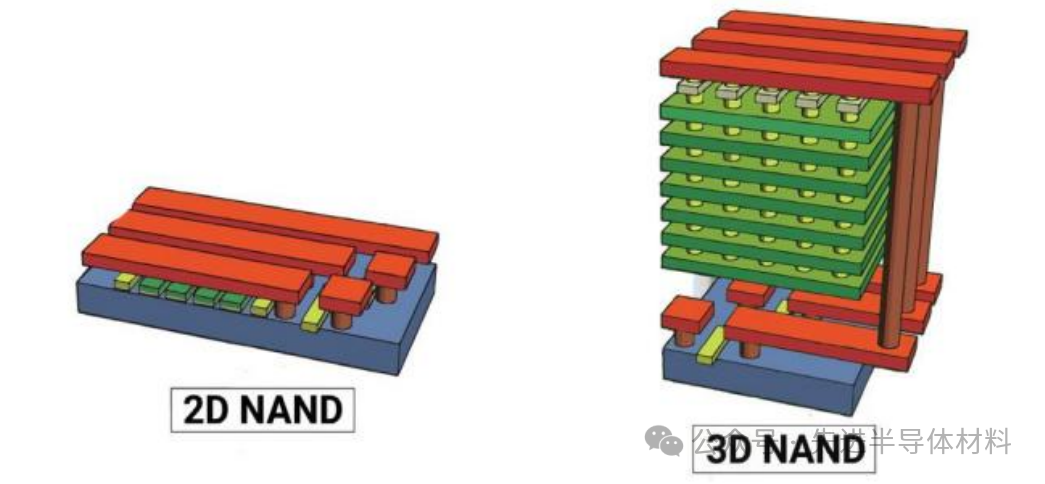

隨先進制程的不斷突破,刻蝕次數顯著增加。在摩爾定律推動下,元器件集成度的大幅提高要求集成電路線寬不斷縮小,制造工序復雜度顯著增加。據 SEMI,20nm 工藝需約 1000 道工序,而 10nm 和 7nm 工藝所需工序已超 1400 道。隨線寬向 10、7、5nm 升級,光刻機精度受波長限制,需采用多重模板工藝,多次薄膜沉積和刻蝕以實現更小線寬,使得刻蝕次數顯著增加,20nm 工藝需刻蝕 50 次左右,而10nm 工藝超 100次,5nm 工藝超 150 次。存儲芯片多層堆疊技術進步,刻蝕技術難度、次數均有所提升。2D結構存儲芯片通過在平面上對晶體管尺寸進行微縮,以獲得更高的存儲密度而當前 2D存儲器件的線寬已接近物理極限,NAND、DRAM內存芯片已進入 3D 時代。3D 結構中,增加集成度的主要方法不再是縮小單層上線寬而是增加堆疊的層數,成功解決 2D 結構增加容量的同時性能降低的問題,實現容量、速度、能效及可靠性等全方位提升。隨層數的增加,芯片加工步驟也同比增加,帶動上游刻蝕設備及對應耗材的需求。

隨先進制程的不斷突破,刻蝕次數顯著增加。在摩爾定律推動下,元器件集成度的大幅提高要求集成電路線寬不斷縮小,制造工序復雜度顯著增加。據 SEMI,20nm 工藝需約 1000 道工序,而 10nm 和 7nm 工藝所需工序已超 1400 道。隨線寬向 10、7、5nm 升級,光刻機精度受波長限制,需采用多重模板工藝,多次薄膜沉積和刻蝕以實現更小線寬,使得刻蝕次數顯著增加,20nm 工藝需刻蝕 50 次左右,而10nm 工藝超 100次,5nm 工藝超 150 次。存儲芯片多層堆疊技術進步,刻蝕技術難度、次數均有所提升。2D結構存儲芯片通過在平面上對晶體管尺寸進行微縮,以獲得更高的存儲密度而當前 2D存儲器件的線寬已接近物理極限,NAND、DRAM內存芯片已進入 3D 時代。3D 結構中,增加集成度的主要方法不再是縮小單層上線寬而是增加堆疊的層數,成功解決 2D 結構增加容量的同時性能降低的問題,實現容量、速度、能效及可靠性等全方位提升。隨層數的增加,芯片加工步驟也同比增加,帶動上游刻蝕設備及對應耗材的需求。

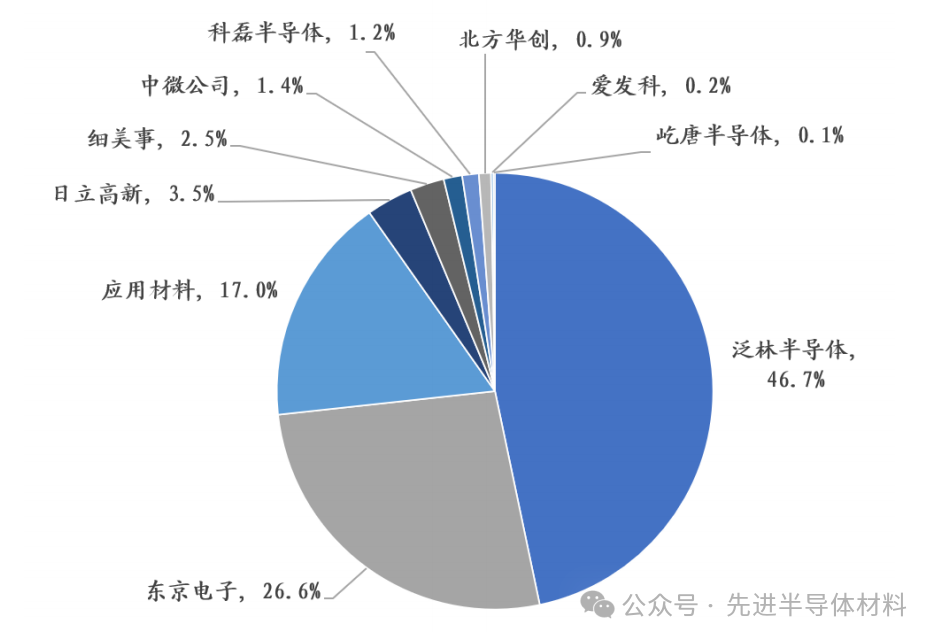

刻蝕設備市場份額情況

來源:先進半導體材料

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。