實驗9:密碼鎖

設(shè)計4位二進制密碼鎖,要求如下:

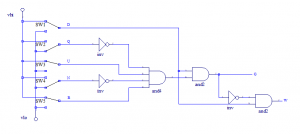

4位密碼輸入代碼分別為Q、U、N、B,開箱時,鑰匙插入鑰匙孔右旋使D=1,如果輸入密碼(如:QUNB=0101)與設(shè)置的代碼相同,則保險箱被打開,即輸出端G=1,否則箱體發(fā)出報警。

根據(jù)任務(wù)要求可知,只有當D=1,且輸入密碼=0101時,輸出G=1,報警器W=0。其他情況下D=1,輸出G=0,報警器W=1。若D=0, 輸出G=0,報警器W=0。密碼鎖真值表如下:

4位密碼鎖程序清單codedlock.v

<code verilog> module codedlock

(

input wire q,u,n,b, //四位開關(guān)作為密碼輸入

input wire d, //一位按鍵作為開鎖使能信號

output wire led1, //保險箱打開信號對應(yīng)的led輸出

output wire led2 //報警信號對應(yīng)的led輸出

);

wire [3:0] code; //四位變量存儲密碼

reg open; //保險箱開箱信號

reg alarm; //報警信號

assign code = {q,u,n,b};

always@(d or code)

if(d == 1'b1) //使能,開始判斷密碼

begin

if(code == 4'b0101)

begin

open = 1'b1; //開鎖

alarm = 1'b0; //沒報警

end

else

begin

open = 1'b0;

alarm = 1'b1;

end

end

else

begin

open = 1'b0;

end

assign led1 = ~open; //led亮表示密碼鎖沒開

assign led2 = ~alarm; //led亮代表發(fā)出報警信號

endmodule

</code>*博客內(nèi)容為網(wǎng)友個人發(fā)布,僅代表博主個人觀點,如有侵權(quán)請聯(lián)系工作人員刪除。