一文了解CPU是如何實現存儲的

為了了解CPU如何獲得其處理能力,讓檢查CPU的實際功能以及它與數據的接口方式。在數字電子學中,一切都由二進制“位”表示。它是兩種可能狀態的基本表示。一個位可以表示零或一,對或錯、向上或向下、接通或斷開、關閉或任何其他雙向值。

在CPU中,“位”在物理上作為電壓電平傳輸。如果我們將多個“位”組合在一起,我們現在可以表示離散狀態的更多組合。例如,如果我們將八位組合在一起,我們形成所謂的字節。一個字節可以代表256個不同的狀態,可以是用于表示數字。對于字節,可以表示0到255之間的任何數字。但是在CPU中,我們如何選擇表示數據完全具有延展性。同一字節也可以代表-128到127之間的數字。該字節的其他表達可能是顏色或聲音級別。當我們將多個字節組合在一起時,我們創建所謂的單詞。單詞以其位容量表示。創建處理器時,其要處理的本機字長構成其架構的核心。原始的Intel 4004處理器以4位字運行。這意味著通過CPU傳輸的數據會傳入一次四位的大塊。通過使用更大的字長,我們可以表示更多的離散狀態因此數量更大。在所有表格中,數據可以帶入CPU內部,其中最重要的是一個是指令。指令是數據的唯一位,它們被解碼并由CPU作為操作執行。一個常見指令的示例是添加兩個單詞一起取值或從一個位置移動一個數據字記憶到另一個位置。

CPU支持的指令的完整列表稱為它的指令集。每條指令的二進制表示形式,其機器通常為代碼分配人類可讀的表示形式被稱為匯編語言。如果我們看大多數CPU的指令集,它們都傾向于專注于對數據執行數學或邏輯運算,測試條件或將其從一個位置移動到內存中的另一個位置。出于所有目的和目的,我們可以將CPU視為指令處理機。

他們通過以下三個基本步驟進行操作,獲取,解碼和執行。隨著CPU設計的發展,這三個步驟變得更加復雜并實施了擴展此核心運營模式的技術。但是,為了充分欣賞這些進步,讓我們先探索一下基本的CPU操作機制。

今天被稱為“經典的精簡指令集計算機”或[RISC]管道”,這種范例構成了第一個CPU的基礎設計。在提取階段,CPU加載它將執行的指令被執行。可以將CPU視為存在于信息氣泡中。它從自身外部提取指令和數據,執行操作在自己的內部環境中,然后將數據返回。此數據通常存儲在CPU外部的內存中,該內存稱為隨機存取存儲器或[RAM]。軟件指令和數據從以下位置加載到RAM中更多永久性資源。

當CPU加載一個數據字時,它通過請求RAM中某個位置的內容。這稱為數據的地址。確定一次CPU可以處理的數據量通過其地址容量。例如,一個4位地址只能直接尋址16個數據位置。存在用于處理比CPU地址容量更多的數據的機制,但現在暫時忽略這些。數據來回移動到RAM的機制稱為總線。CPU和RAM的每一位數據都有自己的通道,以容納數據字和地址字。這些分別稱為數據總線和地址總線。當CPU發出RAM訪問請求時,將進行內存控制CPU的區域將存儲字加載到地址總線解決它希望訪問的地址。然后,它觸發一條控制線,該信號線發出存儲器讀取請求。收到此請求后,RAM用內容填充數據總線所請求的內存位置。現在,CPU在總線上看到此數據。使用CPU將數據寫入RAM的工作方式類似而是發布到數據總線。當RAM收到“寫”信號時,數據內容總線被寫入地址總線所指向的RAM位置。要提取的存儲位置的地址存儲在CPU中,在一種稱為寄存器的機制中。寄存器是一個高速內部存儲器字,它被用作寄存器。CPU操作的“記事本”。通常用作說明的臨時數據存儲但也可以分配給重要的CPU功能,例如跟蹤正在RAM中訪問的當前地址。由于它們是先天設計在CPU硬件中的,因此大多數只有少數幾個寄存器。

它們的字長通常與CPU的本機體系結構耦合。一旦將一個內存字讀入CPU,用于存儲的寄存器該字的地址(稱為程序計數器)將增加。在下一次提取時,它將按順序檢索下一條指令。從RAM訪問數據通常是CPU操作的瓶頸。這是由于需要與組件接口與CPU物理距離較遠。在較舊的CPU上,這并不是什么大問題,但是因為它們變得更快,內存訪問的延遲成為一個關鍵問題。提取指令后,解碼階段便開始。在經典的RISC架構中,一個字的存儲形式完整的說明。隨著CPU的發展,這種方法變得更加復雜。

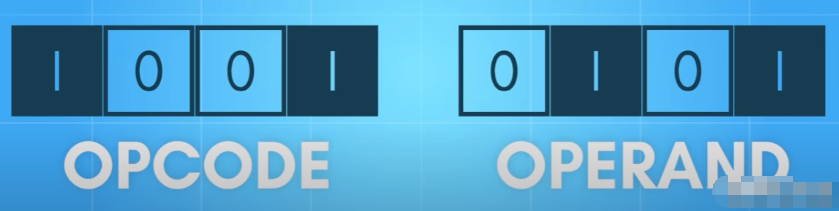

解碼指令時,單詞被分解為兩個部分稱為位域。這些稱為操作碼和操作數。操作碼是代表特定字符的唯一的一系列CPU內的功能。操作碼通常會指示CPU將數據移至寄存器,然后移至寄存器和存儲器之間的數據,執行數學或邏輯功能在寄存器和分支上。當指令引起指令改變時發生分支程序計數器的地址。這將導致下一次獲取在內存中的新位置處發生反對到下一個順序地址。當確保“跳轉”到新程序位置時,稱為無條件分支。在其他情況下,可以進行測試以確定是否應該發生“跳躍”。這稱為條件分支。觸發這些條件的測試通常是數學上的,如果寄存器或內存位置小于或大于一個數字,或者為零或非零。分支允許程序做出決定,并且可以對CPU的功能至關重要。操作碼有時需要數據來對其執行操作。指令的這一部分稱為操作數。操作數是背負在指令上的位,用作數據。在某些指令中,操作數未指定其值自我,但包含要訪問的內存中某個位置的地址。這在請求存儲字的操作碼中很常見加載到寄存器中。這被稱為尋址,并且可以得到更多。

在現代CPU中很復雜。由于以下原因,尋址可能會導致性能下降。需要“離開” CPU,但是隨著CPU設計的進步,這種情況得以緩解。一旦有了操作碼和操作數,操作碼就可以通過表格和電路的組合,然后由控制單元進行配置CPU的各個操作部分以執行該操作。在某些現代CPU中,解碼階段不是硬連線的,可以編程。這允許更改指令的解碼方式以及CPU被配置為執行。在執行階段,將觸發現在配置的CPU這可能會在一個步驟或一系列步驟中發生取決于操作碼。

CPU執行中最常用的部分之一是算術邏輯單元或ALU。該電路塊旨在接收兩個操作數,并且對它們執行基本算術或按位邏輯運算。然后將結果與相應的數學公式一起輸出標志,例如結轉,溢出或零結果。然后將ALU的輸出發送到寄存器或位置根據操作碼在內存中。假設一條指令要求將10加到寄存器中將結果放入該寄存器。

CPU的控制單元將加載立即值指令進入ALU,將寄存器的值加載到ALU中并連接ALU輸出到寄存器。在執行觸發器上,添加完成并輸出加載到寄存器中。實際上,軟件精簡到配置循環在CPU中相互交互的多組電路。在CPU中,這三個階段的操作連續不斷地循環,使其工作通過指令的方式將計算機程序加載到內存中。將這臺打環機粘合在一起是一個時鐘。時鐘是重復脈沖,用于同步CPU內部機械及其與外部組件的接口。CPU時鐘速率是通過每秒的脈沖數或赫茲來衡量的。英特爾4004以740 KHz或每秒740,000脈沖的速度運行。現代CPU可以達到接近5GHz的時鐘速率,或者每秒50億個脈沖。

在較簡單的CPU上,單個時鐘會觸發時鐘的提前。獲取,解碼和執行階段。隨著CPU變得越來越復雜,這些階段可能需要花費幾個時間時鐘周期完成。CPU的吞吐量,可以執行的指令量一秒鐘確定它有多“快”。通過提高時鐘頻率,我們可以使處理器運行通過其階段更快。但是,隨著我們變得越來越快,我們遇到了一個新問題。時鐘周期之間的周期必須留出足夠的時間用于執行的每種可能的指令組合。如果在指令周期之前發生新的時鐘脈沖完成,結果變得不可預測,并且程序失敗。此外,增加時鐘速率具有增加的副作用。功耗和CPU中的熱量積聚導致文化績效的下降。更快,更高效地運行CPU的戰斗主導了它的整個存在。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。