- 電路的功能為了把大范圍的信號電平壓縮顯示,可使用對數電路,通常稱對數放大器,在電氣電路中多使用以10為底的常用對數,本電路是1V/十進位、即10倍的變化引起1V變化輸出的電路。對數作為除法、乘法等運算電路的基本

- 關鍵字:

IP 對數 轉換電路

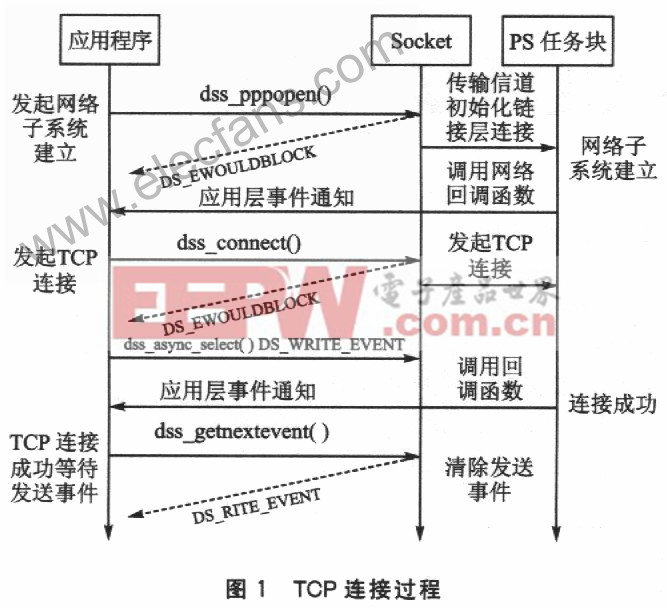

- CDMA是無線通信領域的后起之秀,采用頻分編碼技術,與基于時分復用的GSM相比具有明顯優勢。CDMA能夠實現從現有通信系統到下一代通信系統的平滑過渡,具有較強的功能伸縮性;可以支持先進的天線技術,通過增加小區覆蓋

- 關鍵字:

協議 介紹 IP TCP 無線 終端 CDMA

- 本文介紹了IP4776CZ38主要特性和優勢, 功能方框圖, HDMI發送器和接收器應用框圖以及PCB布局方案框圖.NXP公司的IP4776CZ38是全集成的HDMI接口器件,集成了電平轉移,ESD和背驅保護等功能. IP4776CZ38和HDMI 1.3兼容,每路

- 關鍵字:

4776 HDMI IP 38

- 結合工程實踐,介紹了一種利用FFT IP Core實現FFT的方法,設計能同時對兩路實數序列進行256點FFT運算,并對轉換結果進行求模平方運算,且對數據具有連續處理的能力。設計采用低成本的FPGA實現,具有成本低、性能高、

- 關鍵字:

FFT Core IP 算法

- 如果適配器模塊是由NI公司開發的,那么不需要任何VHDL或其他硬件描述語言的經驗。所有的FPGA編程均通過NI LabVIEW FPGA模塊和NI-RIO驅動程序軟件以圖形化的方式完成。如果該適配器模塊是由第三方開發的,則或許提供定

- 關鍵字:

FlexRIO Verilog VHDL IP

- 在計算機整合制造業(CIM)或工業自動化(IA)領域,許多控制設備進行長距離的數據傳送時有困難,抗干擾性能不好,多 ...

- 關鍵字:

TCP IP 遠程網絡 步進電機 控制器

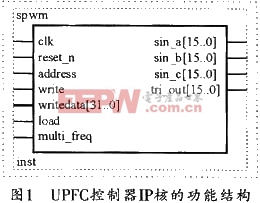

- 0 引言 統一潮流控制器(Unified Power Flow Con-troller,簡稱UPFC)是一種可以較大范圍地控制電流使之按指定路經流動的設備,它可在保證輸電線輸送容量接近熱穩定極限的同時又不至于過負荷。控制系統是UPFC的核

- 關鍵字:

IP 設計 控制器 UPFC FPGA 基于

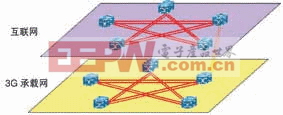

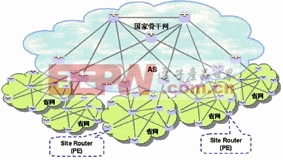

- 毋庸置疑,現代通信網絡的發展,是由業務需求和市場需求來決定的,而不是技術的發展。我們回頭看看互聯網(IP網絡)的發展歷程,這其中市場推動的痕跡非常明顯:這一種六七十年代就已經誕生的IP網絡技術,在九十年代

- 關鍵字:

探討 規劃設計 網絡 承載 IP

- 摘要 為降低FPGA實現3電平SVPWM算法的復雜性,減小SVPWM模塊所占用的資源,文中利用正弦函數和余弦函數的關系,采用小容量ROM提出了一種新的SVPWM控制算法。利用Verilog HDL實現了算法的硬件設計,并封裝成IP核以方便

- 關鍵字:

SVPWM Nios Core IP

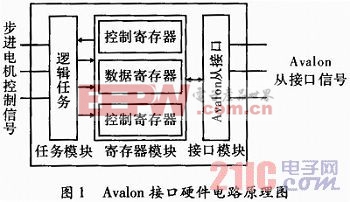

- 摘要 根據Nios II處理器的Avalon總線規范,設計了一款面向步進電機的控制器IP核。該定制IP核采用軟、硬件協同設計的方法,功能符合Avalon總線的讀寫傳輸時序,具有完備的步進電機驅動能力。仿真結果表明,該IP核具有

- 關鍵字:

IP 設計 實現 控制器 電機 Nios II 步進 基于

- 毋庸置疑,現代通信網絡的發展,是由業務需求和市場需求來決定的,而不是技術的發展。我們回頭看看互聯網(IP網絡)的發展歷程,這其中市場推動的痕跡非常明顯:這一種六七十年代就已經誕生的IP網絡技術,在九十年代

- 關鍵字:

分析 規劃設計 網絡 承載 IP

- ATM可以提供空前的可伸縮性和性價比,以及對將來的實時業務、多媒體業務等的支持,ATM將扮演重要的角色。但目前的信息體系,即LAN和WAN,建立在網絡層協議如IP、IPX、AppleTalk等的基礎上,因此,ATM的成功及Internet

- 關鍵字:

技術 介紹 兼容 IP 網絡 ATM

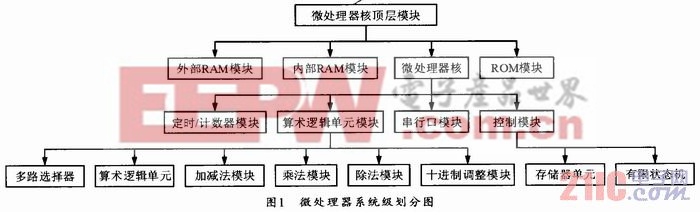

- 基于IP復用和SOC技術的微處理器FSPLCSOC模塊設計,1 引言 文中采用IP核復用方法和SOC技術基于AVR 8位微處理器AT90S1200IP Core設計專用PLC微處理器FSPLCSOC模塊。隨著芯片集成程度的飛速提高,IC產業中形成了以片上系統SOC(System-on-Chip)技術為主的設計方式。一

- 關鍵字:

FSPLCSOC 模塊 設計 微處理器 技術 IP 復用 SOC 基于

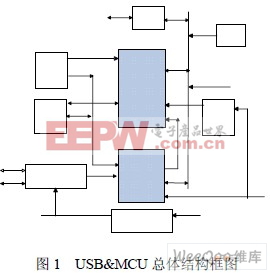

- MCUUSB設備控制器IP核的設計,摘要:用硬件描述語言verilog HDL設計實現了一種MCUUSB設備控制器IP核。論文首先簡要介紹了設計的背景,重點對自主研發的將MCUUSB控制器集成于一個芯片的設計和研究分析。最后給出nc-verilog功能仿真方案以及FPGA驗

- 關鍵字:

設計 IP 控制器 設備 MCU&USB

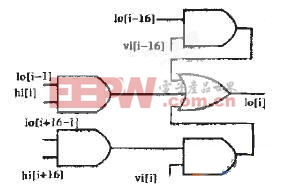

- 嵌入式微處理器IP core設計與分析,摘要:本文在對傳統微控制器進行系統分析的基礎上,提出了一種較好的改進設計方法。回避了傳統微控制器基于累加器的ALU結構及算術邏輯指令:并在指令執行時序上盡量減少指令執行所需的時鐘周期。通過仿真驗證證明該設

- 關鍵字:

設計 分析 core IP 微處理器 嵌入式

neo npu ip介紹

您好,目前還沒有人創建詞條neo npu ip!

歡迎您創建該詞條,闡述對neo npu ip的理解,并與今后在此搜索neo npu ip的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473