dpu asic 文章 最新資訊

ASIC設(shè)計(jì)中不可忽視的幾大問題

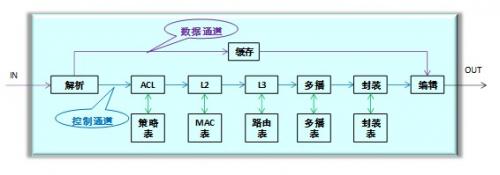

- ASIC的復(fù)雜性不斷提高,同時(shí)工藝在不斷地改進(jìn),如何在較短的時(shí)間內(nèi)開發(fā)一個(gè)穩(wěn)定的可重用的ASIC芯片的設(shè)計(jì),并且一次性流片成功,這需要一個(gè)成熟的ASIC的設(shè)計(jì)方法和開發(fā)流程。 本文結(jié)合NCverilog,DesignCompile,Astro等ASIC設(shè)計(jì)所用到的EDA軟件,從工藝獨(dú)立性、系統(tǒng)的穩(wěn)定性、復(fù)雜性的角度對(duì)比各種ASIC的設(shè)計(jì)方法,介紹了在編碼設(shè)計(jì)、綜合設(shè)計(jì)、靜態(tài)時(shí)序分析和時(shí)序仿真等階段經(jīng)常忽視的問題以及避免的辦法,從而使得整個(gè)設(shè)計(jì)具有可控性。

- 關(guān)鍵字: ASIC

便攜式數(shù)據(jù)采集系統(tǒng)中ADC的選用指南

- 真實(shí)世界的應(yīng)用需要真實(shí)世界的物理連接,一般來說,這意味著模擬信號(hào)要在系統(tǒng)內(nèi)的某處被數(shù)字化處理,以便于微處理器、ASIC或FPGA采集數(shù)據(jù)并做出決策。基本選用標(biāo)準(zhǔn)當(dāng)選擇一款模擬數(shù)字轉(zhuǎn)換器(ADC)時(shí),大多數(shù)設(shè)計(jì)師似

- 關(guān)鍵字: 模數(shù)轉(zhuǎn)換器 SPI ASIC ADC

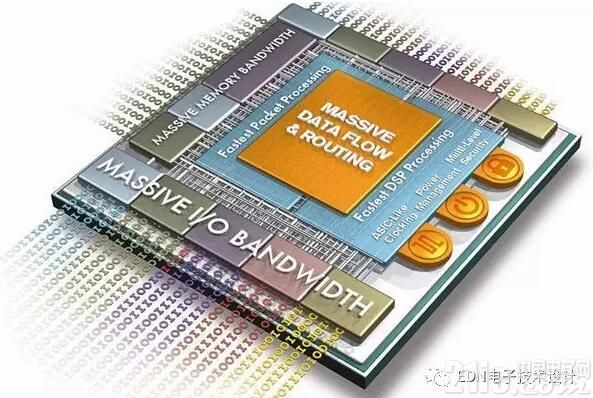

常見問題解答:賽靈思采用首個(gè)ASIC級(jí)UltraScale可編程架構(gòu)

- 1. 賽靈思將在2013年7月10日宣布推出什么產(chǎn)品? 賽靈思宣布20nm兩項(xiàng)新的行業(yè)第一,延續(xù)28nm工藝節(jié)點(diǎn)上一系列業(yè)界創(chuàng)新優(yōu)勢: middot; 賽靈思宣布開始投片半導(dǎo)體行業(yè)首款20nm器件以及投片PLD行業(yè)首款20nm All

- 關(guān)鍵字: UltraScale ASIC 賽靈思 可編程

在系統(tǒng)設(shè)計(jì)中的如何選擇半導(dǎo)體器件:ASIC,還是FPGA?

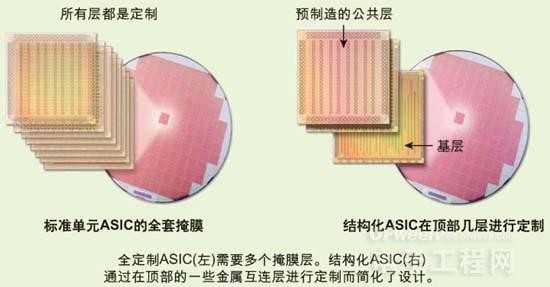

- 作為一個(gè)系統(tǒng)設(shè)計(jì)工程師,經(jīng)常會(huì)遇到這個(gè)問題:是選用ASIC還是FPGA?讓我們來看一看這兩者有什么不同。所謂ASIC,是專用集成電路(Application Specific Integrated Circuit)的簡稱,電子產(chǎn)品中,應(yīng)用非常廣泛。ASIC的

- 關(guān)鍵字: FPGA ASIC 系統(tǒng)設(shè)計(jì) 成本因素

智原發(fā)表PowerSlash(TM)硅智財(cái)于聯(lián)電55奈米超低功耗製程支援物聯(lián)網(wǎng)應(yīng)用開發(fā)

- 聯(lián)華電子今(12日)與ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)共同發(fā)表智原科技于聯(lián)電55奈米超低功耗製程(55ULP)的PowerSlash™基礎(chǔ)IP方案。智原PowerSlash™與聯(lián)電製程技術(shù)相互結(jié)合設(shè)計(jì),為超低功耗的無線應(yīng)用需求技術(shù)進(jìn)行優(yōu)化,滿足無線物聯(lián)網(wǎng)產(chǎn)品的電池長期壽命需求。 智原科技行銷暨投資副總于德旬表示:「物聯(lián)網(wǎng)應(yīng)用建構(gòu)過程中,效能往往受制于低功耗技術(shù)。而今透過聯(lián)電55奈

- 關(guān)鍵字: 聯(lián)華電子 ASIC

智原榮獲ISO9001 Plus品質(zhì)知識(shí)典范獎(jiǎng),高經(jīng)營品質(zhì)打造設(shè)計(jì)服務(wù)

- ASIC 設(shè)計(jì)服務(wù)暨 IP 研發(fā)銷售領(lǐng)導(dǎo)廠商-智原科技(Faraday Technology, TAIEX: 3035)于日前獲頒 ISO9001 Plus 典范獎(jiǎng)項(xiàng)。ISO9001:2015是ISO 15年來最大改版,能成為首批獲得SGS專業(yè)驗(yàn)證的廠商,是對(duì)智原在品質(zhì)承諾、經(jīng)營與職能發(fā)展表現(xiàn)上的高度肯定和最具體驗(yàn)證。 智原科技成立于1993年,累積20余年在 IP (矽智財(cái))與 ASIC 設(shè)計(jì)服務(wù)的豐富經(jīng)驗(yàn),不但自主產(chǎn)出了3,000多支的 IP,更有2,000多個(gè)專案的成功量產(chǎn)經(jīng)驗(yàn),客戶遍及臺(tái)

- 關(guān)鍵字: ASIC 智原科技

智原和聯(lián)電發(fā)表28HPC(U) 12.5G SerDes PHY IP解決方案

- 聯(lián)華電子今(3日) 與 ASIC 設(shè)計(jì)服務(wù)暨 IP 研發(fā)銷售廠商智原科技共同發(fā)表智原科技于聯(lián)電28奈米 HPCU 工藝的可編程12.5Gbps SerDes PHY IP 方案。此次智原成功推出的 SerDes PHY,為聯(lián)電28奈米 High-K / Metal Gate 后閘極技術(shù)工藝平臺(tái)中一系列高速 I/O 解決方案的第一步。 藉由采用涵蓋1.25Gbps 到12.5Gbps 的可編程架構(gòu)技術(shù),此 SerDes PHY 能夠輕易支持10G/1G xPON 被動(dòng)光纖網(wǎng)絡(luò)通訊設(shè)備。結(jié)合不同的

- 關(guān)鍵字: 聯(lián)華電子 ASIC

數(shù)字電路(fpga/asic)設(shè)計(jì)入門之靜態(tài)時(shí)序分析

- 靜態(tài)時(shí)序分析簡稱STA(Static Timming Analysis),它提供了一種針對(duì)大規(guī)模門級(jí)電路進(jìn)行時(shí)序驗(yàn)證的有效方法。它指需要更具電路網(wǎng)表的拓?fù)洌涂梢詸z查電路設(shè)計(jì)中所有路徑的時(shí)序特性,測試電路的覆蓋率理論上可以達(dá)到100%,從而保證時(shí)序驗(yàn)證的完備性;同時(shí)由于不需要測試向量,所以STA驗(yàn)證所需時(shí)間遠(yuǎn)小于門級(jí)仿真時(shí)間。但是,靜態(tài)時(shí)序分析也有自己的弱點(diǎn),它無法驗(yàn)證電路功能的正確性,所以這一點(diǎn)必須由RTL級(jí)的功能仿真來保證,門級(jí)網(wǎng)表功能的正確性可以用門級(jí)仿真技術(shù),也可以用后面講到的形式驗(yàn)證技術(shù)。值

- 關(guān)鍵字: fpga asic 靜態(tài)時(shí)序

關(guān)于除法電路

- 除法,這個(gè)小學(xué)4年紀(jì)就開始學(xué)習(xí)和使用的方法卻一直是我這個(gè)ASIC工程師心中的痛。我一直在思考如何能找到一個(gè)簡單(硬件資源少)而快捷(時(shí)鐘排數(shù)少)的通用除法電路。 其實(shí)簡單的說除法可以用迭代的減法來實(shí)現(xiàn),但是對(duì)于硬件,這恐怕要花很多時(shí)間。我也一直沒有找到實(shí)現(xiàn)任意除法的好方法。但是對(duì)于某些除數(shù)固定的除法還是有一些辦法的。 1)最容易想到的就是ROM查找表,但是ROM畢竟不是我們的目標(biāo),雖然ROM有時(shí)是不錯(cuò)的方法。 2)我開始仔細(xì)考慮這個(gè)問題是在做264解碼時(shí)必須要處理QP的問題。這是一個(gè)除以6的計(jì)算

- 關(guān)鍵字: 除法電路 ASIC

Mentor Graphics Veloce VirtuaLAB增加針對(duì)領(lǐng)先網(wǎng)絡(luò)設(shè)計(jì)的下一代協(xié)議

- 2015年10月19日,Mentor Graphics公司今天宣布,推出支持25G、50G和100G以太網(wǎng)的Veloce® VirtuaLAB Ethernet環(huán)境。這種支持有助于實(shí)現(xiàn)今天正在創(chuàng)建的基于大規(guī)模以太網(wǎng)設(shè)計(jì)的高效的、基于仿真的驗(yàn)證。 連接需求的激增對(duì)交換機(jī)和路由器設(shè)計(jì)的尺寸有著深遠(yuǎn)的影響,使之成為了今天開發(fā)的最大的IC設(shè)計(jì)。設(shè)計(jì)的絕對(duì)尺寸、早期發(fā)布的壓力,以及需要驗(yàn)證所有路徑,都推動(dòng)著將驗(yàn)證從模擬轉(zhuǎn)向基于仿真流程方法的轉(zhuǎn)變。 Juniper Networks硅和系統(tǒng)工程

- 關(guān)鍵字: Mentor Graphics ASIC

FPGA實(shí)戰(zhàn)演練邏輯篇:FPGA與ASIC

- 拋開FPGA不提,大家一定都很熟悉ASIC。所謂ASIC,即專用集成電路(Application Specific Integrated Circuit)的簡稱,電子產(chǎn)品中,它無所不在,還真是比FPGA普及得多得多。但是ASIC的功能相對(duì)固定,它是為了專一功能而生,希望對(duì)它進(jìn)行任何的功能和性能的改善往往是無濟(jì)于事的。打個(gè)淺顯的比喻,如圖1.2所示,如果說ASIC是布滿鉛字的印刷品,那么FPGA就是可以自由發(fā)揮的白紙一張。(特權(quán)同學(xué)版權(quán)所有) ? 圖1.2 ASIC和FPG

- 關(guān)鍵字: FPGA ASIC

dpu asic介紹

您好,目前還沒有人創(chuàng)建詞條dpu asic!

歡迎您創(chuàng)建該詞條,闡述對(duì)dpu asic的理解,并與今后在此搜索dpu asic的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)dpu asic的理解,并與今后在此搜索dpu asic的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司