基于Xtensa的ASIP開發(fā)流程研究

(1)將C++代碼輸入Tensilica Xplorer開發(fā)環(huán)境,選擇系統(tǒng)自帶的sample_config-params (RB-2006.0)配置信息作為ASIP開發(fā)的起點(diǎn),即在此基礎(chǔ)上進(jìn)行體系結(jié)構(gòu)的調(diào)整和指令的自定義開發(fā)。

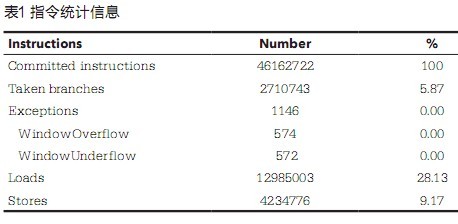

本文引用地址:http://www.czjhyjcfj.com/article/95269.htm(2) 運(yùn)行代碼并進(jìn)行特性分析(Profile),表1和表2是最基本的指令和時(shí)鐘周期信息,此外還可以得到pipeline甘特圖、Branch cycle和Interlock cycle對(duì)比圖等信息。這些信息為后續(xù)的體系結(jié)構(gòu)調(diào)整和指令優(yōu)化提供了必要的數(shù)據(jù)依據(jù)。

(3) 調(diào)整處理器配置信息中的眾多項(xiàng)目,如MUL16 / MUL32 / MAC、Zero-overhead loop instructions、Pipeline length、Number of coprocessors、Floating point coprocessor、Special register、Cache size等,設(shè)計(jì)者可以得到圖3所示的速度、面積、功耗信息。然后回到(2)再次運(yùn)行代碼及特性分析,考察體系結(jié)構(gòu)改動(dòng)帶來的影響。

(4)利用XPRES工具,設(shè)置FLIX的Issue Width、SIMD的Vector Length、Register的Depth / Width / Ports、Fusion的Area / Latency / Operands等,XPRES會(huì)自動(dòng)生成若干種不同的自定義指令TIE供設(shè)計(jì)者選擇使用。設(shè)計(jì)者參考每一個(gè)TIE的Cycles和Gates數(shù)折衷考慮,當(dāng)然設(shè)計(jì)者還可以手動(dòng)增加TIE指令。然后將TIE綁定到調(diào)整后的體系結(jié)構(gòu)(配置信息)上,回到(2)運(yùn)行代碼及特性分析,考察TIE帶來的性能提高效果。

評(píng)論