Spartan-3 FPGA系列中高效PCB布局的LVDS信號倒相

輸入 DDR 示例

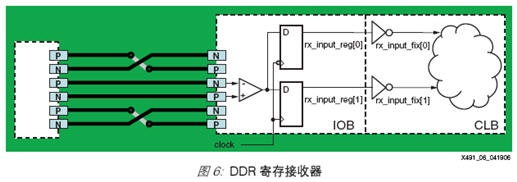

本文引用地址:http://www.czjhyjcfj.com/article/86182.htm圖 6 所示為接收 DDR 方案,其中每條輸入線生成兩條可能需要倒相的內部數據線。對于Spartan-3E FPGA 的 DDR 輸入,推薦使用新型的 IDDR2 輸入觸發器結構。這種結構去除了從下降沿到下一上升沿的所有通路,從而可以使內部邏輯更容易設計。要了解有關 IDDR2 的詳情,請參閱 DS312 《Spartan-3E FPGA 系列數據手冊》。

以下代碼說明針對相同生成環示例的 DDR 寄存接收器情況。唯一的變化是增加了 Spartan-3E FPGA 的 IDDR2 例示。原 Spartan-3 器件需要略微不同的代碼,因為它不包含 IDDR2 結構。

所附 ZIP 文件包含完整細節(請參閱“設計文件”)。

Verilog 語言代碼:

.

parameter [2:0] SWAP_MASK = 3'b010;

.

.

genvar i;

generate

for (i = 0; i <= 2; i = i + 1)

begin: loop0

IBUFDS#(.IOSTANDARD("LVDS_25"), .IFD_DELAY_VALUE("0"), .DIFF_TERM("FALSE"))

ibuf_d (.I(datain_p[i]), .IB(datain_n[i]), .O(rx_input[i]));

IDDR2 #(.DDR_ALIGNMENT("C0")) fd_ioc(.C0(clkin), .C1(notclk), .D(rx_input[i]),

.CE(1'b1), .R(1'b0), .S(1'b0), .Q0(rx_input_reg[i+3]),

.Q1(rx_input_reg[i]));

assign rx_input_fix[i] = rx_input_reg[i] ^ SWAP_MASK[i];

assign rx_input_fix[i+3] = rx_input_reg[i+3] ^ SWAP_MASK[i];

end

endgenerate

VHDL 語言代碼:

.

constant SWAP_MASK : std_logic_vector(2 downto 0):= "010";

.

.

loop0: for i in 0 to 2 generate

ibuf_d : ibufds

generic map (IOSTANDARD => "LVDS_25", IFD_DELAY_VALUE => "0", DIFF_TERM => FALSE)

port map (i => datain_p(i), iB => datain_n(i), o => rx_input(i));

fd_d : iddr2

generic map (DDR_ALIGNMENT => "C0")

port map (c0 => clkin, c1 => notclock, d => rx_input(i), ce => '1', r => '0',

s => '0', q0 => rx_input_reg(i+3), q1 => rx_input_reg(i));

rx_input_fix(i) <= rx_input_reg(i) xor SWAP_MASK(i);

rx_input_fix(i+3) <= rx_input_reg(i+3) xor SWAP_MASK(i);

通過修改紅色的粗體字符,可以方便地將此機制擴展到不同的位寬。

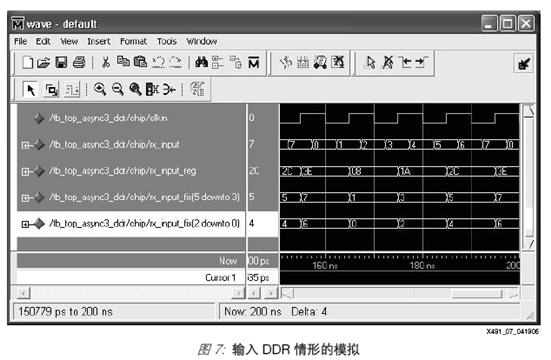

在使用 DDR 技術時,位操作可能很重要。DDR 生成環示例生成一條總線,總線的低階位聚集在時鐘的下降沿,而其高階位則聚集在下一個上升沿。圖7 是 DDR 設計模擬運行的屏幕截圖,其中顯示了這種位集中現象。此模擬運行假設所有跡線都是正確的(即沒有進行引腳交換),以清楚地顯示具體位的結束位置。

輸出 DDR 示例

圖8 所示為發射器的 DDR 方案,其中每對發送數據線由 Spartan-3E FPGA 中的 ODDR2(在Spartan-3 FPGA 中是 FDDRRSE)機制進行多路復用。這種情況下,在與極性需要倒相的LVDS 輸出相關聯的每條線路中都增加了倒相器。因為這些倒相器在上述實現過程中被吸收到輸出觸發器中,所以它們不會改變電路的時序。

以下代碼說明生成環示例的發射器 DDR 寄存情形。原 Spartan-3 器件需要略微不同的代碼,因為它不包含 ODDR2 結構。所附 ZIP 文件包含完整細節(請參閱“設計文件”)。

Verilog 語言代碼:

parameter [2:0] SWAP_MASK = 3'b010 ;

genvar i ;

generate

for (i = 0 ; i <= 2 ; i = i + 1)

begin : loop0

OBUFDS #(.IOSTANDARD("LVDS_25"))

obuf_d (.I(tx_output_reg[i]), .O(dataout_p[i]), .OB(dataout_n[i]));

ODDR2 #(.DDR_ALIGNMENT("NONE")) fd_ioc (.C0(clkin), .C1(notclk),

.D0(tx_output_fix[i+3]), .D1(tx_output_fix[i]), .CE(1'b1), .R(1'b0),

.S(1'b0), .Q(tx_output_reg[i])) ;

assign tx_output_fix[i] = tx_output[i] ^ SWAP_MASK[i] ;

assign tx_output_fix[i+3] = tx_output[i+3] ^ SWAP_MASK[i] ;

end

endgenerate

VHDL 語言代碼:

constant SWAP_MASK : std_logic_vector(2 downto 0) := "010" ;

loop0 : for i in 0 to 2 generate

ibuf_d : obufds generic map (IOSTANDARD => "LVDS_25")

port map (i => tx_output_reg(i), o => dataout_p(i ), oB =>

dataout_n(i));

fd_d : oddr2 generic map (DDR_ALIGNMENT => "NONE")

port map (c0 => clkin, c1 => notclock, d0 => tx_output_fix(i),

d1 => tx_output_fix(i+3), ce => '1', r => '0', s => '0', q =>

tx_output_reg(i));

tx_output_fix(i) <= tx_output(i) xor SWAP_MASK(i) ;

tx_output_fix(i+3) <= tx_output(i+3) xor SWAP_MASK(i) ;

end generate ;

通過修改紅色的粗體字符,可以方便地將此機制擴展到不同的位寬。

如上所述,在使用 DDR 技術時,位操作可能很重要。DDR 生成環示例生成一條總線,總線的低階位在時鐘的下降沿上發送,而其高階位則在下一個上升沿上發送。

設計文件

本應用指南介紹的各種接收器和發射器示例的設計文件是針對所有 Spartan-3 器件和

Spartan-3E 系列器件編寫的。可從 Xilinx 網站 (xapp491.zip) 獲得 Verilog 和 VHDL 兩種語言的設計文件。所附 readme.txt 文件提供了最新詳情。

結論

用 LVDS 進行設計時,有計劃地謹慎使用 Spartan-3 FPGA 系列資源,可以大幅度降低 PCB 布局的復雜性,同時可以提高整體電路板信號的完整性。對于器件中集成的 LVDS 接收器和LVDS 發射器來說也是如此,但輸入時鐘引腳除外;輸入時鐘引腳必須具有正確的極性。

評論