基于PCI總線的GP-IB接口電路設計

NAT9914接口控制電路主要完成內部總線到外設的時序控制。GP-IB總線接口采用的是負邏輯電平設計,考慮到EPLD的容量有限,在設計時數據傳輸不支持DMA模式,只支持單周期CPU讀寫。由于CPU讀數據時延遲較大,在對PCI狀態機設計時必須進行讀延遲等待。

狀態機的設計與實現

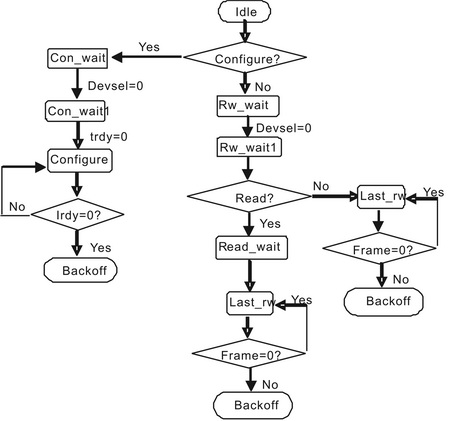

狀態機的設計是整個設計中的核心部分,它主要用來控制從設備和PCI總線的時序。在本設計方案中,配置過程的完成和存儲器的讀寫都是由狀態機來完成的。由于EPLD的容量有限,GP-IB接口芯片的讀寫速度比較慢,在設計狀態機時,不支持CPU的猝發操作。表1給出了狀態機的狀態名、狀態變量和說明,圖3給出了狀態機的流程圖。

圖3 狀態機設計流程圖

下面根據狀態機的流程圖給出讀、寫操作時序分析與設計要點:

PCI規范中定義了三種讀寫操作,即Memory和I/O讀寫及配置讀寫。本方案不支持I/O讀寫,只支持Memory和配置的讀寫,下面給出Memory映射方式的單周期仿真讀寫時序。

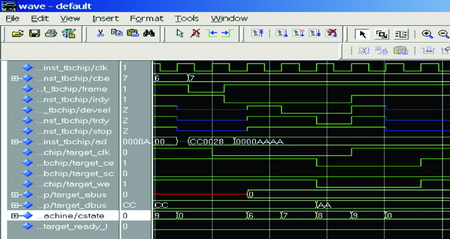

存儲器寫操作

存儲器單周期寫操作時序如圖4所示,當frame為低電平時啟動讀寫操作,同時給出要寫的目標地址ad[31..0]和命令cbe[3..0]=7,cbe等于7表示寫寄存器,從設備鎖存命令和地址到緩沖區。在第2個clk,主設備將irdy變低,同時給出數據,狀態機運行到6,鎖存數據給緩沖區,trdy、devsel由高阻變為高電平。在第3個clk,devsel變低,給出主設備應答信號,表示從設備已經響應請求,狀態機運行到7。根據寫操作,target_we、target_ce變低,并對地址進行譯碼,放在地址總線上,同時驅動數據總線,表示在對控制芯片進行寫操作。在第4個clk,檢測到目標設備的target_ready_l為低電平,表示從設備已經做好接受數據的準備,狀態機運行到8,將trdy變低。在第5個clk,狀態機運行到9,trdy變高,同時主設備將驅動irdy變高,表示一個寫周期結束。狀態機運行到初始狀態,等待下一次操作。target_ce、target_we將延遲變高,結束控制芯片寫周期。

圖4 存儲器寫周期時序

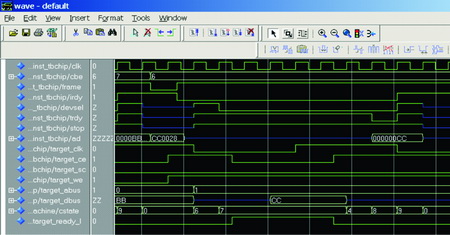

存儲器讀操作

存儲器單周期讀操作時序如圖5所示,當frame為低電平時啟動讀寫操作,同時給出要寫的目標地址ad[31..0]和命令cbe[3..0]=6,從設備鎖存該命令和地址。在第2個clk,狀態機運行到6,進入讀寫等待狀態,主設備將frame變高,表示單周期模式,trdy、devsel、由高阻變為高電平。在第3個clk,狀態機運行到7,并給出應答信號devsel,檢測到target_ready_l為高電平,狀態機進入等待狀態,直到為低電平,然后運行到讀等待狀態4。在狀態機8,trdy變低,從設備將讀數據放在ad[31..0]總線上。在狀態機9,trdy變高,devsel變高,同時主設備將irdy變高,結束單周期讀操作。devsel、trdy回到高阻狀態,狀態機運行到初始狀態,準備下次操作。

圖5 存儲器讀周期時序

結語

本設計占用芯片的資源少,可移植性強,根據設備不同的需求可以進行設計更改,在很多測試儀器中都得到了廣泛的應用。

參考文獻:

1.李貴山、陳金鵬,PCI局部總線及其應用,西安電子科技大學出版社,2003

2. 候伯亨、顧新,VHDL硬件描述語言與電路設計,西安電子科技大學出版社,1997

評論