一種用于高速ADC的采樣保持電源電路的設計

在電路的輸入端加一個正弦波信號(Vpp為2 V,頻率為10 MHz),輸出端在保持相時能在4 ns內穩定到1 V,這滿足100 MHz采樣頻率的要求。

將該OTA應用到圖3所示的采樣保持電路中,輸入幅值為1 V的差分正弦信號,輸出信號如圖6所示。由圖可知,保持值與輸入信號的采樣值之間的差值小于0.3 mV.對于10位精度的ADC來說,采樣保持的誤差應該小于

即0.488 mV.因此該采樣保持電路可以應用于10位ADC中。

測量動態特性最直接的方法是對其輸出做快速傅里葉變換(FFT)。無雜散動態范圍(spurious freedynamic range,SFDR)是衡量動態性能的一個重要的技術指標。SFDR是指所能處理的最大和最小信號之比。它與輸入信號的幅度無關,因此,用它表示的動態性能更具有普遍意義。

圖7(a)和(b)分別是在采樣頻率為100 MHz下,對由輸入信號為5.1758 MHz和47.9492 MHz(約為奈奎斯特采樣頻率)的滿幅度正弦信號(Vpp=2 V)所得的輸出信號的FFT頻譜圖。

式中:fin是輸入頻率;fs是采樣頻率;Nwindow是記錄的正弦波的周期數,它必須是一個質數。測量FFT的頻譜圖可知當輸入信號fin=5.175 8 MHz時,SFDR為81 dB;當輸入信號fin=47.949 2 MHz(約為奈奎斯特采樣頻率)時,SFDR為80 dB.

結論

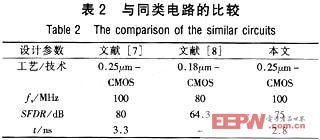

本文設計了一個可應用于10位、100 MS/s流水線ADC前端模塊的采樣保持電路。采用增益提升技術使得采樣保持電路中的OTA達到100 dB的增益,并且GBW達到1 GHz,達到0.05%精度的建立時間小于4 ns.采用上述OTA的采樣保持電路在100 MHz采樣頻率下,當輸入信號的頻率為5.175 8MHz時,SFDR為81 dB.當輸入信號的頻率為47.949 2 MHz(約為奈奎斯特采樣頻率)時,SFDR為80 dB.與近期國內外同類電路進行比較,比較結果如表2所示。由表2可知,該采樣保持電路在性能上還是不錯的。

評論