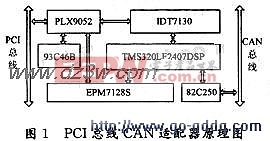

基于PCI軟“核”的PCI總線接口設計與實現

STOP_USR 是STOP信號的“克隆”版本。

CFG_HIT 表明一個有效的配置周期開始。

ADDR_VLD 表明當前作業地址線的起始地址有效。

S_SRC_EN 在Slave模式讀操作期間,告訴用戶模塊驅動下一片數據到總線ADIO[31:0]上。

S_DATA_VLD 表明當前ADIO[31:0]上的數據為有效數據(在Slave模式下)。

BASE_HIT[7:0] 表明基地址寄存器譯碼并選中相應的PCI映射空間。

CFG[255:0] PCI設備配置空間接口信號。

M_SRC_EN 在寫操作時,表明數據源可以驅動下一片數據到ADIO[31:0]上(在INItiator模式下)。

M_DATA_VLD 表明當前數據線ADIO[31:0]上的數據為有效數據(在Initiator模式下)。

REQUEST 在主設備模式下,DMA控制器請求系統仲裁器讓出總線。

M_WRDN 在主設備模式下,當前的作業進行讀操作或寫操作。M_WRDN=1時表示寫,M_WRDN=0時表示讀。

M_DBE[3:0] 在主設備模式下,驅動總線命令和字節有效信號。

COMPLETE 在主設備模式下,當前的DMA方式傳送數據完成。

M-DMTA 表示在Initiator模式下當前主設備正片于數據周期。

DR_BUS 表示主設備狀態機正驅動PCI總線。

I_IDLE 表示主設備狀態機正在空閑狀態,當前PCI總線沒有被驅動。

M_ADDR_USR 表示主設備狀態機在地址周期要求驅動地址信號到ADIO[31:0]上。

RST PCI總線復位信號的“克隆”版本。

CLK 由系統緩沖區驅動的PCI總線時鐘。

INTER_USR 由用戶發出的中斷請求信號。是INTR_A信號的“克隆”版本。

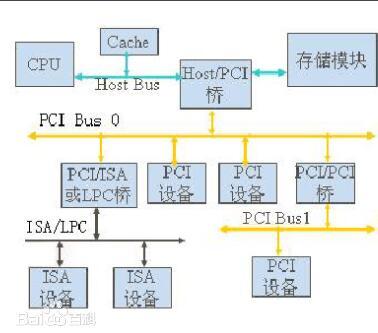

從LogiCore提供的接口看出,該軟“核”將復雜的PCI接口按照PCI的兩種工作模式轉化成相對簡單的Slave和Master兩組獨立接口信號。用戶可以根據實際需要來確定的應用那種模式,從而選用相應的一組或兩組信號作為接口。而且LogiCore這種橋梁作用只是對PCI功能進行劃分,它將PCI控制器的核心邏輯留給用戶來實現,并給出狀態機的接口信號。

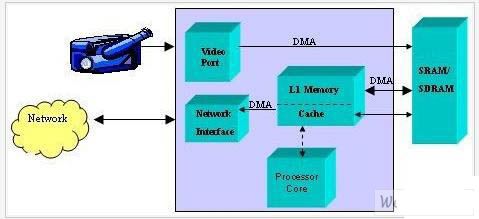

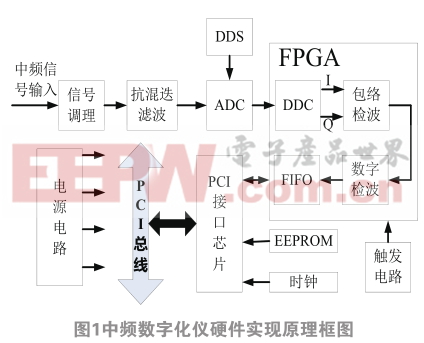

2 PCI Master控制器的實現

以一個基于PCI總線的數據采集卡為例說明利用LogiCore實現PCI Master控制器的方法。由PCI協議知道,當PCI設備工作在Master模式下,可以直接訪問計算機系統主存儲器,而不通過計算機CPU。為此,在PCI Master控制器中必須設計一個DMA控制器。這樣同主存儲器傳送數據時,可以暫時接管系統總線,控制傳送字節數,判斷DMA傳輸是否結束,發出DMA結束等信號來保證數據的正確傳送。該數據采集卡所實現的功能就是不斷從外部接收數據并以DMA方式輸入到計算機系統緩沖區中,同時將預先放在計算機內存中的大量數據以DMA方式輸出到外部的儀器中。DMA控制器屬于LogiCore邏輯框圖中的用戶控制模塊。它由現行字節數寄存器、現行地址寄存器、基字節數寄存器、基地址寄存器、半滿地址寄存器、全滿地址寄存器、狀態寄存器、讀寫緩沖器及控制寄存器和優先級編碼器等組成、DMA控制器原理圖如圖3所示。其中控制寄存器和優先級編碼器是DMA控制器的關鍵。

2.1 DMA控制器的特點

(1)現行地址寄存器、基字節數寄存器、基地址寄存器、半滿地址寄存器、全滿地址寄存器5個寄存器可由高層應用程序根據當前驅動程序分配的系統內存空間來靈活配置。當傳送完規定的傳送長度(字節數減到零時),結束當前DMA傳送并自動重新對現行地址寄存器進行初始化,具有自動初始化能力。

(2)優先級編碼器中的4個DMA請求源的優先級是固定的,不可以旋轉。優先級按照從高到低依次為讀緩沖器、STATUS_C(由狀態寄存器C-D發出的)、寫緩沖器、STATUS_D(由狀態寄存器C-D發出的)。

優先權編碼器對4個DMA請求源進行優先級編碼,并向LogiCore發出DMA請求信號。

(3)DMA數據傳送有單字節傳送和數據塊傳送兩種方式。數據塊傳送方式可由用戶初始化基字節寄存器來靈活設置一次傳送的數據塊長度。DMA控制器向系統緩沖區發送狀態寄存器C-D中的信息時采用單字節傳送方式。而傳送讀緩沖器和寫緩存器中的數據時采用數據塊傳送方式并可由用戶設置一次傳送數據的長度。此時每傳送一個數據,地址指針加1,字節數據1。

(4)DMA控制器中讀緩沖器和寫緩沖器都是2KB。

2.2 DMA控制器基本工作原理

2.2 DMA控制器基本工作原理

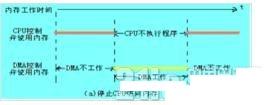

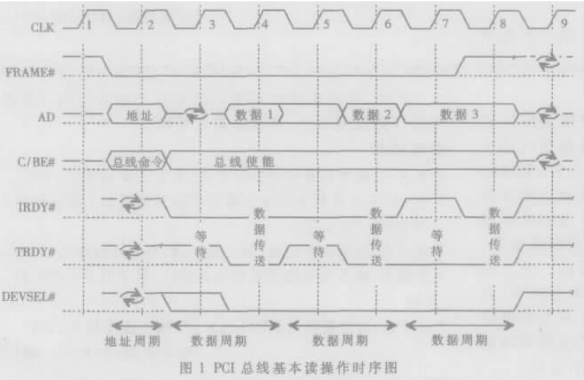

首先由高層應用程序根據采集卡的低層驅動程序分配的系統內存地址對基地址寄存器、半滿地址寄存器、全滿地址寄存器、狀態寄存器、讀寫緩沖器和控制寄存器進行初始化。然后啟動系統,開始工作。當讀緩沖器的數據量不到半滿或寫緩沖器中接收到的數據量已超過半滿或狀態寄存器C-D有狀態信息向高層報告時,則向優先級編碼器發出相應的請求信號。DMA優先級編碼器根據DMA請求對象的操作類型向DMA控制寄存器發出相應的控制信號。當DMA控制器檢索到對應的控制信息發生變化時,向LogiCore發出DMA請求,并用基字節寄存器和基地址寄存器分別初始化現行字節數寄存器和現行地址寄存器。當計算機系統允許DMA控制器占用PCI總線時,則DMA控制器接管PCI總線,并在地址周期向LogiCore發出DMA讀寫命令,同時輸出當前要對系統緩沖區操作的起始地址。在隨后的數據周期中,從數據總線ADIO上輸出或接收數據,同時修改地址指針(DMA支持隱含尋址)和字節計數器值,DMA控制器檢測傳送是否結束。如未結束則不停循環傳送。當檢測到字節計數器即將為零時,則向LogiCore發出COMPLETE信號,COMPLETE信號持續到字節計數器為零時,DMA控制器釋放掉對PCI總線的控制權,使CPU恢復正常工作狀態。

在DMA控制器中,狀態寄存器C-D有兩個DMA請求源STATUS_C和STATUS_D。其中STATUS_C在地址比較器檢測到讀緩沖器讀完對應系統緩沖區一半空間或全部讀守對應系統緩沖區數據時,置相應的狀態信息并向優先級編碼器發出STATUS_C請求信號。而STATUS_D在地址比較器檢測到寫緩沖器寫完對應系統緩沖區數據、置相應的狀態信息并向優先級編碼器發出STATUS_D的請求信號。

值和注意的是,在DMA控制器設計過程中,當進行數據塊傳輸、字節數寄存器計數快結束時,應提前向計算機系統發出完成本次數據塊傳送的COMPLETE信號,這樣可保證DMA數據塊傳送的正確進行。至于提前幾個字節數據可以根據試驗來確定,一般提前2~4個字節即可。

PCI總線設計中定義的雙向信號,均要用OE信號來控制。同時有些信號如地址比較等要進行分割,以使用最少的通用邏輯模塊數來實現。這些是PCI總線設計所要注意的事項。由于LogiCore中對這些情況在邏輯上已經進行優化處理,從而使用戶避免了同復雜的PCI接口打交道,減少犯錯誤的可能,縮短了開發周期。

本數據采集卡在WINDOWS 98多任務操作系統下運行數據傳輸速率可以達到140Mbps,滿足了實際要求。

電磁爐相關文章:電磁爐原理

評論