談談旁路和去耦合電容-原理部分

看了很多關于旁路電容和去藕電容的文章,有代表性的如下:

退耦電容的選擇和應用

十說電容

關于旁路電容和耦合電容

關于旁路電容的深度對話

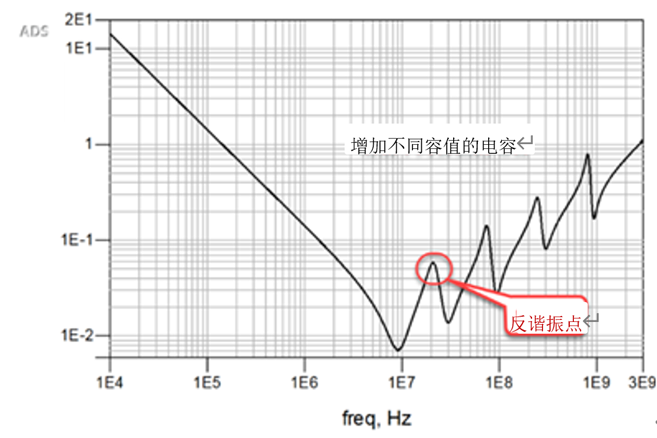

對于以上的文章,我是很佩服的,我按照它們的思路把問題推演和考證了一下,參考了一些數據,自己推導一下電容模型的阻抗曲線,試圖做的就是讓問題更明顯一些。打算把這個問題分成兩個部分,第一個就是原理上去驗證,第二個就是從實際的例子去推演。各位看完有任何意見請留言。

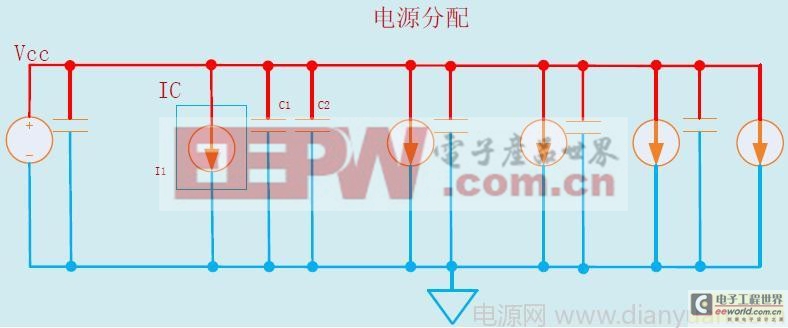

先看看此類電容的應用場合:

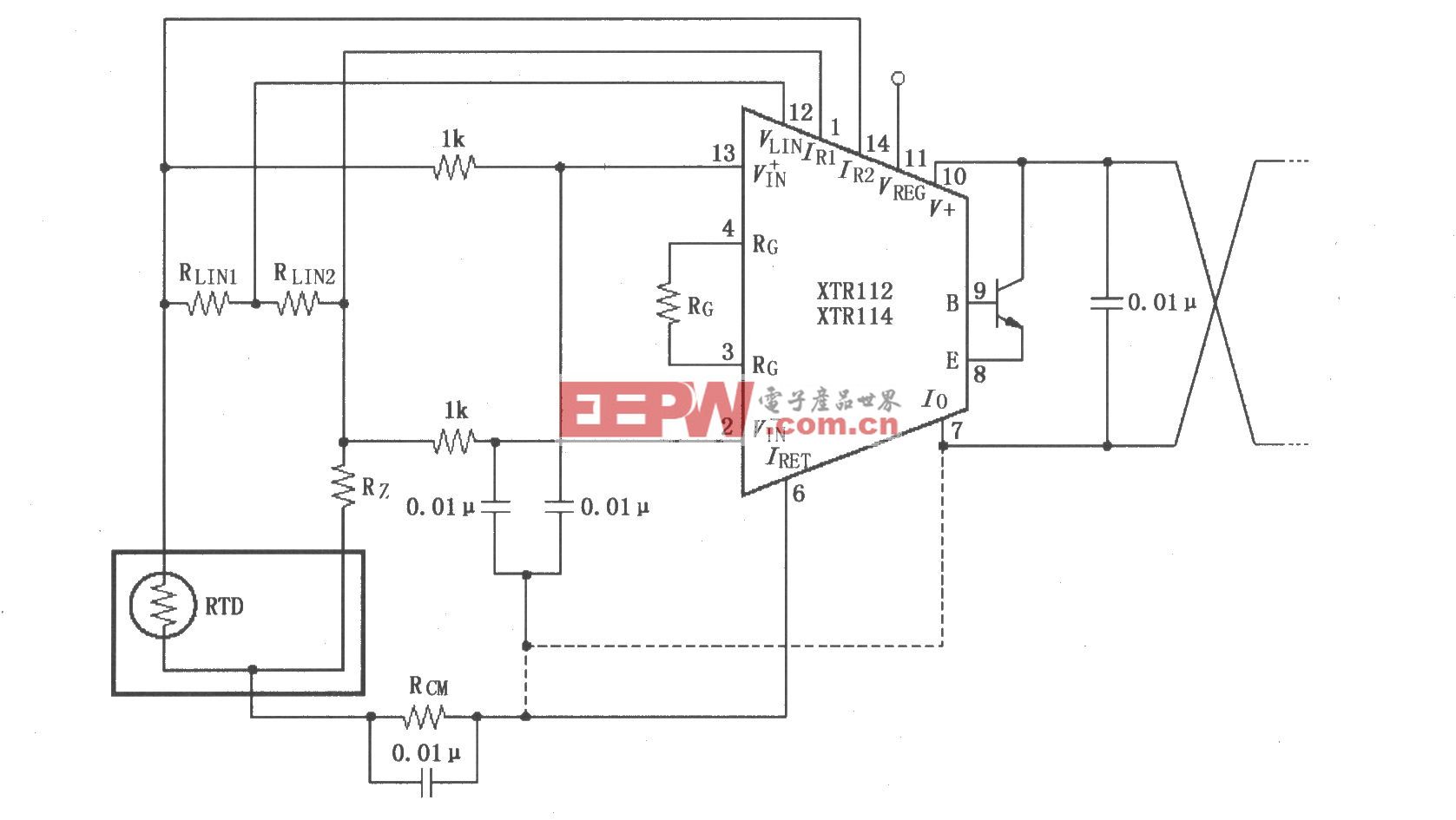

根據以上電路來說,由一個電源驅動多個負載,如果沒有加任何電容,每個負載的電流波動會直接影響某段導線上的電壓。

瞬間沖擊電流的產生原因

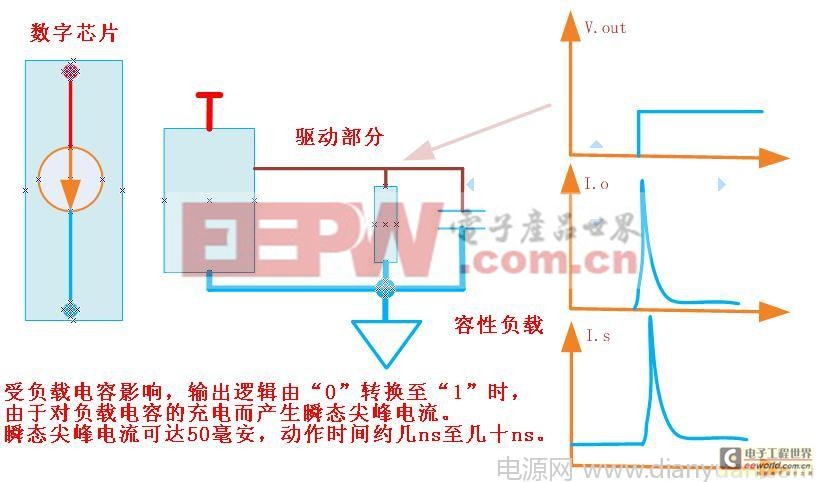

1.容性負載

來分析一下數字電路的電流波動,數字電路的負載并不是純阻性的,如果負載電容比較大,數字電路驅動部分要把負載電容充電、放電,才能完成信號的跳變,在信號上升沿比較陡峭的時候,電流比較大,對于數字芯片來說,新派驅動部分電流會從電源線上吸收很大的電流,由于線路存在著的電感,電阻(特別是芯片管腳上的電感,會產生反彈),這種電流相對于正常情況來說實際上就是一種噪聲,會影響前級的正常工作,下圖反應了工作情況

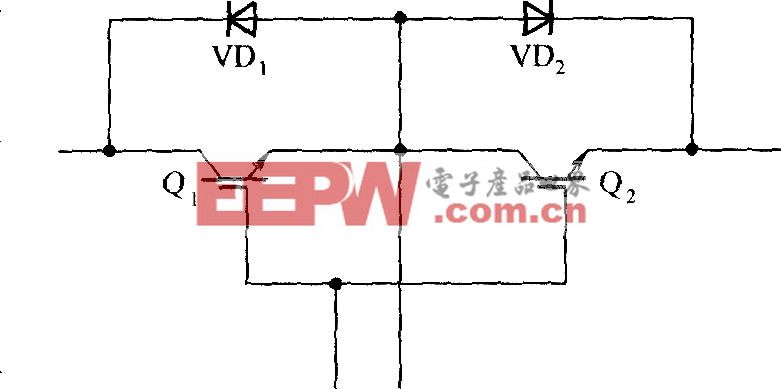

2.輸出級控制正負邏輯輸出的管子短時間同時導通,產生瞬態尖峰電流

PMOS和NMOS同時導通的時候出現的電流尖峰。

電壓塌陷噪聲

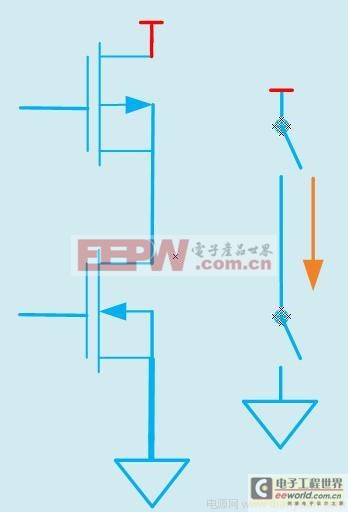

我們考慮數字電路內部結構一般由兩個Mos管組成,為了便于分析,我們假設初始時刻傳輸線上各點的電壓和電流均為零。現在我們分析數字器件某時刻輸出從低電平轉變為高電平,這時候器件就需要從電源管腳吸收電流(上面一個分析的是容性負載,現在考慮的是阻性負載)。

從低到高(L=>H)

在時間點T1,高邊的PMOS管導通,電流從PCB板上流入芯片的VCC管腳,流經封裝電感L.vcc,通過PMOS管和負載電阻最后通過返回路徑。電流在傳輸線網絡上持續一個完整的返回時間,在時間點T2結束。之后整個傳輸線處于電荷充滿狀態,不需要額外流入電流來維持。

當電流瞬間涌過L.vcc時,將在芯片內部電源和PCB板上產生一個電壓被拉低的擾動。該擾動在電源中被稱之為同步開關噪聲(SSN)或Delta I噪聲。

從高到低(L=>H)

在時間點T3,我們首先關閉PMOS管(不會導致脈沖噪聲,PMOS管一直處于導通狀態且沒有電流流過的)。同時我們打開NMOS管,這時傳輸線、地平面、L.gnd以及NMOS管形成一回路,有瞬間電流流過開關NMOS管,這樣芯片內部至PCB地節點前處產生參考電平被抬高的擾動。該擾動在電源系統中被稱之為地彈噪聲(Ground Bounce)。

實際電源系統中存在芯片引腳、PCB走線、電源層、底層等任何互連線都存在一定電感值,就整個電源分布系統來說來說,這就是所謂的電源電壓塌陷噪聲。

電荷放大器相關文章:電荷放大器原理 電容相關文章:電容原理 電子負載相關文章:電子負載原理

評論