MOS芯片的ESD保護電路設計

隨著CMOS集成電路產業的高速發展,越來越多的CMOS芯片應用在各種電子產品中,但在電子產品系統的設計過程中,隨著CMOS工藝尺寸越求越小,單位面積上集成的晶體管越來越多,極大地降低了芯片的成本,提高了芯片的運算速度。

但是,隨著工藝的進步和尺寸的減小,靜電釋放(ESD),Elecyro Static Discharge)問題變得日益嚴峻。據統計,在集成電路設計中大約40%的失效電路是ESD問題造成的。

MOS晶體管是絕緣柵器件,柵極通過薄氧化層和其他電極之間絕緣。如果柵氧化層有較大的電壓,會造成氧化層擊穿,使器件永久破壞。

隨著器件尺寸減少,柵氧化層不斷減薄,氧化層能承受的電壓也不斷下降,引起氧化層本征擊穿的電場強度約為1 X 107V/cm。如柵氧化層厚度是50 nm 則可承受的最大電壓約50 V,當柵氧化層厚度減少到5 nm,則所能承受的最大電壓約為5 V。因此外界的噪聲電壓容易引起柵擊穿。

特別是外界各種雜散電荷會在柵極上積累,由于MOS 晶體管的柵電容很小,只要少量的電荷就能形成很大的等效柵壓,引起器件和電路失效,這就是ESD問題。例如,人體所帶的靜電荷可產生高達幾kV的電壓,在80%的濕度情況下,人走過化纖地毯可能產生1.5 kV靜電壓。ESD對CMOS集成電路的損傷,不僅會引起MOS器件柵擊穿,還可能誘發電路內部發生閂鎖效畸應。

另外,靜電釋放產生的瞬時大電流可能造成芯片局部發熱,損害器件和電路。在一般的條件下,ESD不會導致器件即時失效,它往往潛伏在集成電路器件中,這種存在有潛在缺陷的器件在使用時容易失效。

特別是在深亞微米CMOS工藝中,由于溥柵氧化層的擊穿電壓較低,必須加入有效的在片ESD保護電路以箝位加到內部電路柵氧化層上的過充電壓。

1 ESD放電模式與設計方案

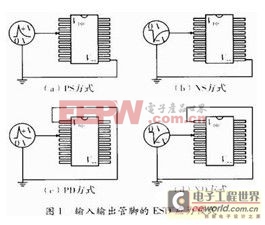

電路的輸入或輸出端與電源和地之間的ESD應力有4種模式

在集成電路中和外界相連的輸入、輸出端子比內部器什更容易受到ESD損傷。一般電路的輸入或輸出端與電源和地之間的ESD應力有4種模式:

(1)某一輸入(或輸出)端對地的正脈沖電壓(PS模式):VSS接地,ESD正電壓加到該輸入輸出端,對VSS放電,VDD與其他管腳懸空。

(2)某一輸入(或輸出)端對地的負脈沖電壓(NS模式):VSS接地,ESD負電壓加到該輸入輸出端,對VSS放電,VDD與其他管腳腳懸空。

(3)某一個輸入或輸出端相對VDD端的正脈沖電壓(PD模式):VDD接地,ESD正電壓加到該輸入輸出端,對VDD放電,VSS與其他管腳懸空。

(4)某一個輸入或輸出端相對VDD端的負脈沖電壓(ND模式):VDD接地,ESD負電壓加在該輸入輸出端,對VDD放電,VSS與其他管腳懸空。

防止集成電路芯片輸入、輸出端受到ESD應力損傷的方法是在芯片的輸入和輸出端增加ESD保護電路。保護電路的作用主要有兩方面:一是提供ESD電流的釋放通路;二是電壓鉗位,防止過大的電壓加到MOS器件上。

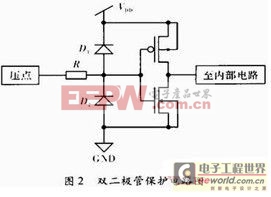

對CMOS集成電路連接到壓點的輸入端常采用雙二極管保護電鍍,圖2所示為常見的ESD保護電路的結構:雙二極管保護電路。

二極管D1是和PMOS源、漏區同時形成的,是p+n-結構,二極管D2是和NMOS源、漏區同時形成的,是n+p-結構。當壓點相對地出現負脈沖應力,則二極管D2導通,導通的二極管和電阻形成ESD電流的泄放通路。

當壓點相對地出現正脈沖應力,使二極管D2擊穿,只要二極管D2擊穿電壓低于柵氧化層的擊穿電壓,就可以起到保護作用。類似的,當壓點相對電源出現正脈沖或負脈沖應力,二極管D1起保護作用,提供靜電荷的泄放通路。

這兩個二極管把加到輸入級MOS晶體管柵極的電壓范圍如式(1)所示:-0.7

假設二極管的正向導通電壓是0.7 V。電阻的作用是限制流過二極管的電流。由于ESD應力電壓都是短暫的脈沖信號,只要電流不是非常大,二極管不會被燒壞,可以持續起保護作用。

圖2中使用二極管作為I/O端的ESD保護電路,主要提供PD和NS模式下的電流泄放通路,但對于ND模式和PS模式,二極管處于反偏狀態,反偏箝位電壓過高,電流泄放能力較弱,導通電阻較高,使箝位能力不夠,且產生的熱量較大。

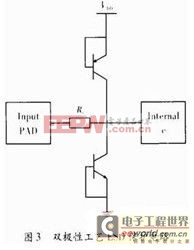

圖3中電路主要用于雙極工藝,采用一個基極接VDD地PNP三極管和一個基極接地的NPN三極管共同構成ESD保護電路。采用這種保護電路,相對于二極管,在ND和PS模式下,可以工作在Snapback狀態,具有較強的電流泄放能力和較低的維持電壓。

2 ESD保護電路

對深亞微米CMOS集成電路,柵氧化層的擊穿電壓很小,常規二極管的擊穿電壓較大,不能起到很好的保護作用。因此可以增加離子注入提高二極管的襯底濃度,形成p+n+和n+p+結構來降低二極管的擊穿電壓。

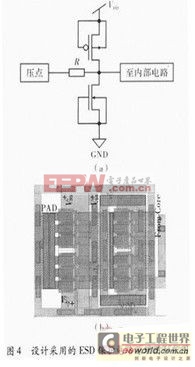

考慮到準備流片的多功能數字芯片要采用CSMC2P2M 0.6μm標準的COMS工藝,在設計中采用了如圖4所示的ESD保護電路,用一個柵接地的NMOS管和一個柵接VDD的PMOS管共同構成輸入ESD保護電路。

另外,由于設計的ESD保護電路的MOS官尺寸大,所以在版圖上畫成多個插指,同時由于保護電路的MOS管尺寸較大,其漏源區pn結又可以起到二極管保護作用。圖4所示為設計采用的ESD保護電路的原理圖和版圖。

圖5所示為一款多功能數字芯片的版圖照片和封裝示意圖,表1為管腳對應圖

在多功能數字芯片的設計中,在輸入端使用了設計的ESD保護電路,另外,由于所設計的多功能數字芯片,在輸出端設計了尺寸較大的MOS管構成的反相器來提高芯片的驅動能力,這些MOS管的漏區和襯底形成的pn結就相當于一個大面積的二極管,可以起到ESD保護作用。

因此,一般可不用增加ESD保護器件,但由于需要在芯片流片后首先進行在片測試,所以在芯片的輸出端加上了與輸入端同樣的ESD保護電路。

3 ESD保護電路在流片后的測試情況

圖6所示為流片后的多功能數字芯片的在片測試波形,由測試波形可以看出,ESD保護電路對多功能數字芯片起到保護作用。

4 結束語

系統介紹了ESD保護電路;分析了不同的傳統ESD保護電路的設計原理和優缺點。在此基礎上,基于CSMC 2P2M 0.6μm標準的COMS工藝,進行ESD保護電路的版圖設計和驗證,并在一款多功能數字芯片上應用,該芯片參與了MPW計劃進行流片。測試結果顯示該ESD保護電路能直接應用到各種集成電路芯片中。

pic相關文章:pic是什么

電流傳感器相關文章:電流傳感器原理

評論