FPGA與ADSP TS201的總線接口設計方案

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。ADI公司的TigerSHARC系列DSP芯片浮點處理性能優越,故基于這類DSP的DSP+FPGA處理系統正廣泛應用于復雜的信號處理領域。同時在這類實時處理系統中,FPGA與DSP芯片之間數據的實時通信至關重要。

TS201 DSP的外部總線接口有兩種協議:慢速協議和高速流水協議。流水線協議適合與快速同步設備連接,文中采用此協議,實現DSP與FPGA之間的通信。

1 DSP流水線協議

流水線協議用來提供流水線方式的數據傳輸。在該傳輸協議下,每個時鐘周期可以傳輸一個數據。控制流水線協議進行數據傳輸的主要信號包含以下引腳:

- RD——數據傳輸讀信號;

- WRH和WRL——數據傳輸寫信號;

- BRST——突發方式數據傳輸指示;

- ADDR——地址總線;

- DATA——數據總線。

流水線協議數據傳輸有兩種方式:普通流水線協議和突發流水線協議。ADSP TS201的數據總線位寬可以通過SYSCON寄存器設置為32位或者64位,但是有時候需要傳輸的數據位寬可能是32位,64位或者128位,這樣就有可能出現數據總線位寬和數據位寬不一致的情況,如果總線位寬小于數據位寬,DSP采用突發流水協議傳輸,否則采用普通流水線協議。

1.1 普通流水線協議

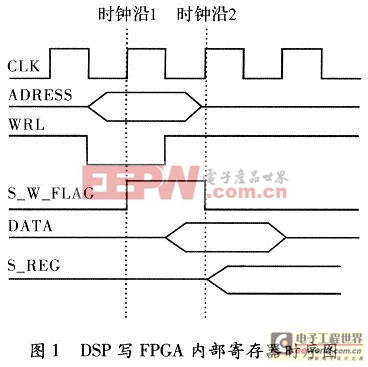

圖1是DSP使用普通流水協議,寫FPGA內部寄存器時序圖,流水深度為1,在時鐘沿1地址線、WRx(WRH和WRL)同時有效,一個時鐘周期后,在時鐘沿2數據線有效,地址線、WRx無效。

評論