用EEPROM對大容量FPGA芯片數據實現串行加載

自大規模現場可編程邏輯器件問世以來,先后出現了兩類器件,一類是基于SRAM體系結構的FPGA系列,如XILINX公司的4000系列和最新的Virtex系列;另一類是基于faxtFLASH技術的CPLD器件,如XILINX公司的9500系列和Lattice公司的ispLSxx系列芯片。FPGA具有容量大、設計資源豐富、片內ROM及RAM設計靈活等特點1,但是它們需要在每次上電時進行數據加載。目前實現加載的方法有以下三種:①采用PROM并行加載;②采用專用SROM串行加載;③采用單片機控制實現加載。第一種方式需要占用較多的FPGA管腳資源,雖然這些管腳在加載完成后可用作一般I/O口,但在加載時不允許這些管腳有其他任何外來信號源;另外數據存儲器PROM與FPGA之間的大量固定連線如8位數據線以及大量訪問PROM的地址線等,使得PCB設計不便。但是第一種方式有一個有利的方面,即PROM的容量較大、容易購置、價格低、技術支持(編程器)較好。第二種方式情況剛好與第一種方式相反,即占用資源少、PCB布板方便,但是容量小、價格較高、兼容性差。第三種方式采用單片機控制,由PROM中讀取并行數據,然后再串行送出。由于涉及到單片機編程,對于開發者來說較為不便;另外,如果單片機僅用來實現該任務,較為浪費硬件資源。CPLD的一個最大優點是采用計算機專用開發工具,通過JTAG口直接一次性實現編程數據加載,并永久保留,除非進行再次編程(與GAL器件相似)。該類器件比較適合在實驗室內進行現場調試,但是由于其數據的加載必須通過計算機,因此對于從事野外作業者來說會產生不便。

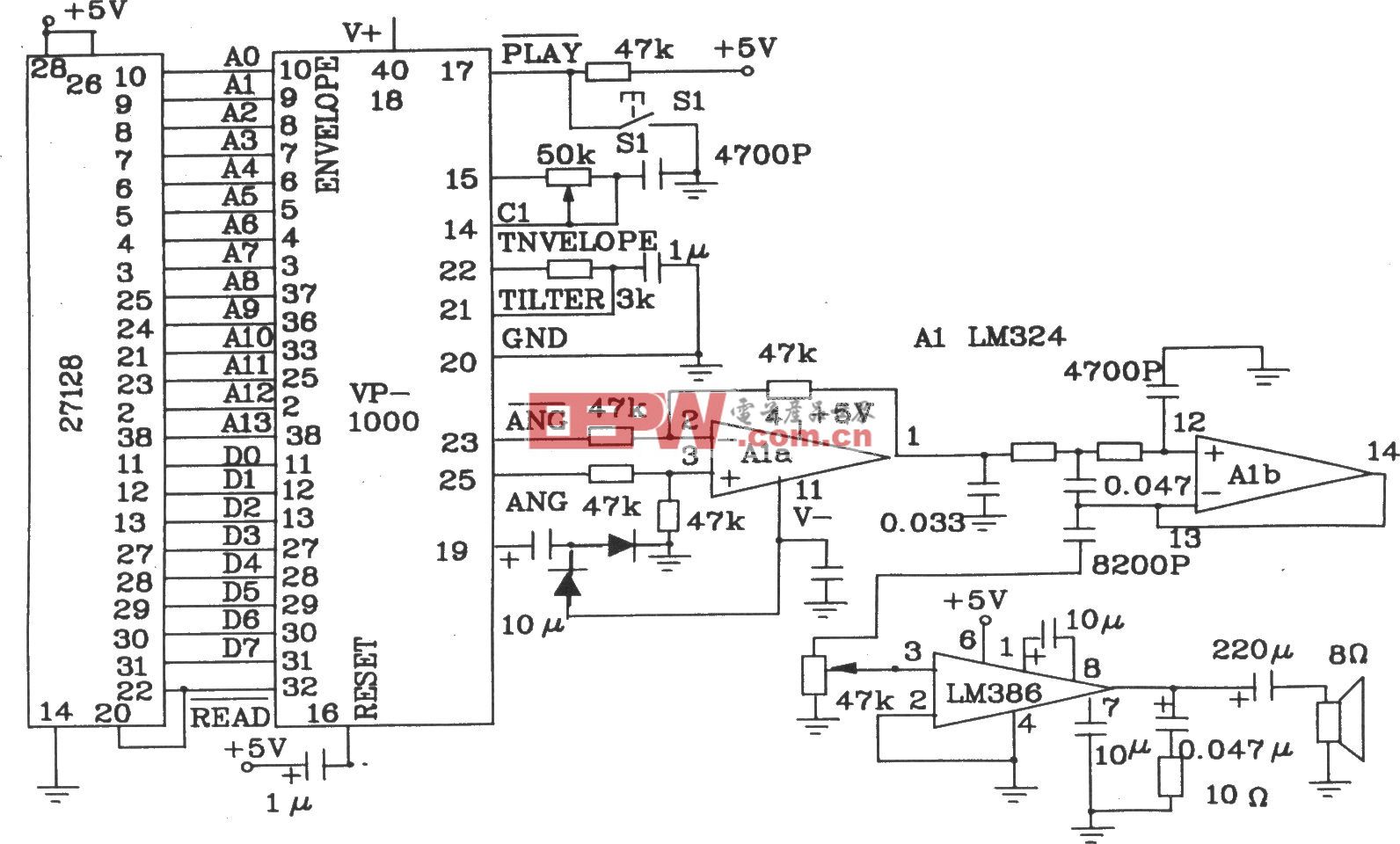

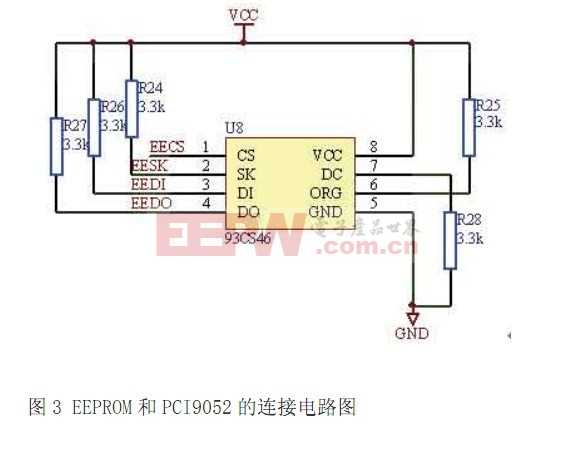

通過上述比較,并結合實際工作情況,我們認為采用串行數據加載比較方便、可靠(這種可靠性得益于FPGA與SROM之間較少的接口線)。但隨著FPGA規模的不斷升級,其CONFIG數據量越來越大,截止到本文寫作時,CONFIG數據量最大已到6MBIT,雖然XILINX公司有相關的XC17X系列SROM提供使用,但皆為一次性芯片2、開發成本較高、代理商供貨周期長、價格較高,這給FPGA的應用及普及帶來很大的障礙。我們曾使用過AT&T公司的ATT17系列電可擦除SROM,但是該類SROM芯片能與XILINX系列FPGA芯片實現接口的種類不多,且容量小。由于種種原因,其價格往往是同樣存儲容量的EEPROM的五、六倍,甚至更高,并且來源困難。那么能不能結合并行加載與串行加載的優點,從而解決大容量FPGA數據加載的問題呢?我們在仔細分析了串行加載機制后,認為采用EEPROM作為數據存儲器,經過可控的并-串轉換,應該可以實現數據加載。下面以XILINX公司Virtex系列XCV100芯片為例,采用ATMEL公司1兆位的AT29C010A進行數據存儲,采用XILINX公司9500系列XC95108芯片作為加載控制器件進行設計。

1 原理設計

原理性Master Serial模式串行加載時序如圖1所示

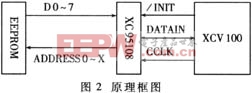

在該加載模式中,比較重要的幾個信號為/INIT、CCLK、DATAIN、DONE。/INIT表示FPGA芯片上電時或者當/PROGRAM信號為低時FPGA內部數據初始化過程,并作為外送信號給數據加載控制器件作為復位之用。當/INIT信號躍為高電平時,CCLK開始啟動。加載數據DATAIN在CCLK的上升沿打入,與通用串行通訊相類似,加載數據流也有開始位與結束位,且以數據幀的方式接收。一旦發生錯誤,FPGA立即停止接收數據,并將/INIT信號置為低電平,因此該信號又稱為錯誤指示信號。當數據全部接受并驗證無誤后,FPGA將DONE信號置為"1"3。 在分析了FPGA加載數據流特性后,可以得出這樣一個結論:保證CCLK與DATAIN之間的嚴格同步與連續性,就可以實現加載。基于此結論,在生成加載數據格式時,產生單片SROM串行格式,對于XILINX公司的FPGA系列,該格式為.MCS文件格式;然后用ALL07編程器以INTEL HEX數據格式將其寫入EEPROM中。余下的工作是在CCLK、/INIT、DATAIN的控制下完成并-串轉換。該控制過程采用一片CPLD之95系列XC95108芯片來承擔,在設計容量上采用一片XC9536即可完成,之所以采用XC95108是因為其尚需要完成其他任務。其原理框圖如圖2所示。

2 并-串轉換時序設計

在時序設計上,關鍵在于要保持DATAIN加載數據的連續性、DATAIN與CCLK加載時鐘的同步性以及EEPROM訪問地址的復位問題。對于復位問題,采用上電時FPGA產生的/INIT信號對95108內部的EEPROM地址發生器復位。這樣做的原因是/INIT與FPGA之CCLK時鐘產生有著同步關系,但同時也默認上電加載是一次成功;在考慮串行DATAIN數據的連續性時,采用兩組移位寄存器,設定它們為R_shiftA和R_shiftB,當R_shiftA在進行移位操作時,R_shiftB由EEPROM中讀入八位并行數據,反之亦然;為保持DATAIN與CCLK時鐘的同步性,所有上述操作都以CCLK為同步時鐘,值得注意的是,由于DATAIN串行數據是在CCLK的上升沿打入FPGA,因此我們給予XC95108芯片設計的運轉時鐘是經過反相的CCLK時鐘,這樣就保證了CCLK與DATAIN的時間關系。

以下是為該加載設計的VHDL硬件編程語言設計程序45,其中的計數器及移位寄存器模塊用F2.11設計軟件之LogicBlox模塊產生。整個程序經F2.1I開發軟件仿真、編譯成功后,經JTAG編程電纜寫入XC95108芯片。加電后便加載成功,經多次加電實驗,成功率為100%。

評論