一種基于FPGA的數字復接系統的設計與實現

引言

數字通信網中,為擴大傳輸容量和提高傳輸效率,常運用數字復接技術,將若干低速碼流合并成高速碼流,通過高速信道傳送。而以往的PDH數字復接系統大多采用模擬電路或傳統ASIC設計,電路復雜龐大且受器件限制,靈活性和穩定性都很低,系統的調試修改難度也很大。近年來可編程器件的應用日益廣泛,使用較多的是現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。FPGA器件性能優越,使用方便,成本低廉,投資風險小,使用FPGA設計可以完全根據設計者需要開發ASIC芯片,可方便地反復編寫和修改程序,即使制成PCB后仍能進行功能修改。本文將著重介紹運用FPGA技術實現基群與二次群之間復接與分接系統的總體設計方案。

數字復接基本原理及系統構成

二次群幀結構及其復接子幀結構

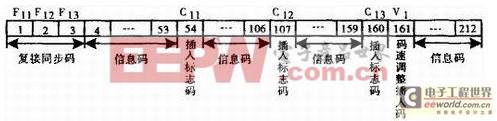

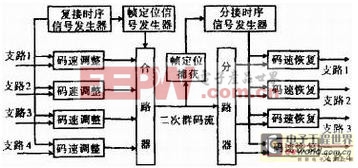

按ITU-TG.742協議,工作在8448kbit/s的采用正碼速調整的二次群復接設備幀結構如圖1所示,一幀共有848bit,前12位幀碼組包括幀同步碼10位,碼型為1111010000;失步對告碼,同步為“0”,失步為“1”;國內通信備用碼。Cj1、Cj2、Cj3(j=1,2,3,4)為插入標志碼,Vj(j=1,2,3,4)為碼速調整插入比特,其作用是調整基群碼速。二次群由四支路的子幀構成,子幀結構如圖2所示,一子幀有212bit,1、2、3位碼為幀碼組,記Fj;插入標志碼用Cj表示;碼速調整插入比特用Vj表示。

圖1 二次群幀結構

圖2 復接子幀結構(以第一條支路為例)

復接系統構成

復接系統構成的框圖如圖3。復接時序信號發生器產生碼速調整需要的時序信號,四路基群信號先各自經正碼速調整,變為2.112Mbit/s的同步碼流。合路器順序循環讀取四路碼流,并在每幀開頭插入幀定位信號,輸出8.448Mbit/s的標準二次群。

圖3 復接的系統構成框圖

在接收端,合路碼流先進行幀定位捕獲,判定系統處于同步態、失步態還是過渡態。一旦捕獲到幀定位信號,便驅動分接時序信號發生器工作,產生分路和碼速恢復需要的時序信號,同時分路器工作,把幀定位信號拋掉,順序循環分別送入4個碼速恢復單元,扣除插入碼元,恢復成四路2.048Mbit/s的基群信號。

評論