H.264/AVC中CAVLC編碼器的硬件設(shè)計實現(xiàn)

H.264/AVC是ITU-T和ISO聯(lián)合發(fā)布的國際視頻壓縮標準[1],比特壓縮率分別是MPEG-4、H.263及MPEG-2的39%、49%及64%[2],是一種高壓縮比的新標準。基于內(nèi)容的自適應(yīng)可變長編碼(CAVLC)是H.264中關(guān)鍵技術(shù)之一,應(yīng)用于H.264的基本檔次和擴展檔次對亮度和色度殘差數(shù)據(jù)塊進行編解碼,編碼效率高,抗誤碼和糾錯能力強[3],但計算復(fù)雜度大,用軟件編碼難以滿足高清視頻實時性要求。H.264編碼過程不涉及任何浮點數(shù)運算,特別適合硬件電路實現(xiàn)。文獻[4]提出的CAVLC編碼可分成掃描和編碼2部分,掃描部分對殘差數(shù)據(jù)zig-zag逆序掃描后,提取出run-level標志以及相關(guān)信息提供給編碼部分進行編碼。文獻[5]對掃描模塊進行了優(yōu)化。編碼模塊中非零系數(shù)級(level)編碼計算量最大,復(fù)雜度最高。本文充分利用FPGA高速實時特點,采用并行處理及流水線設(shè)計,通過優(yōu)化CAVLC編碼結(jié)構(gòu)和level編碼子模塊,提高CAVLC編碼器的性能。

1 CAVLC原理

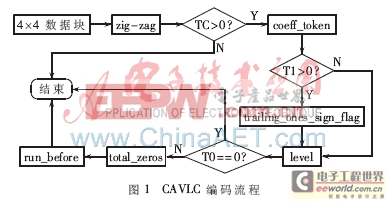

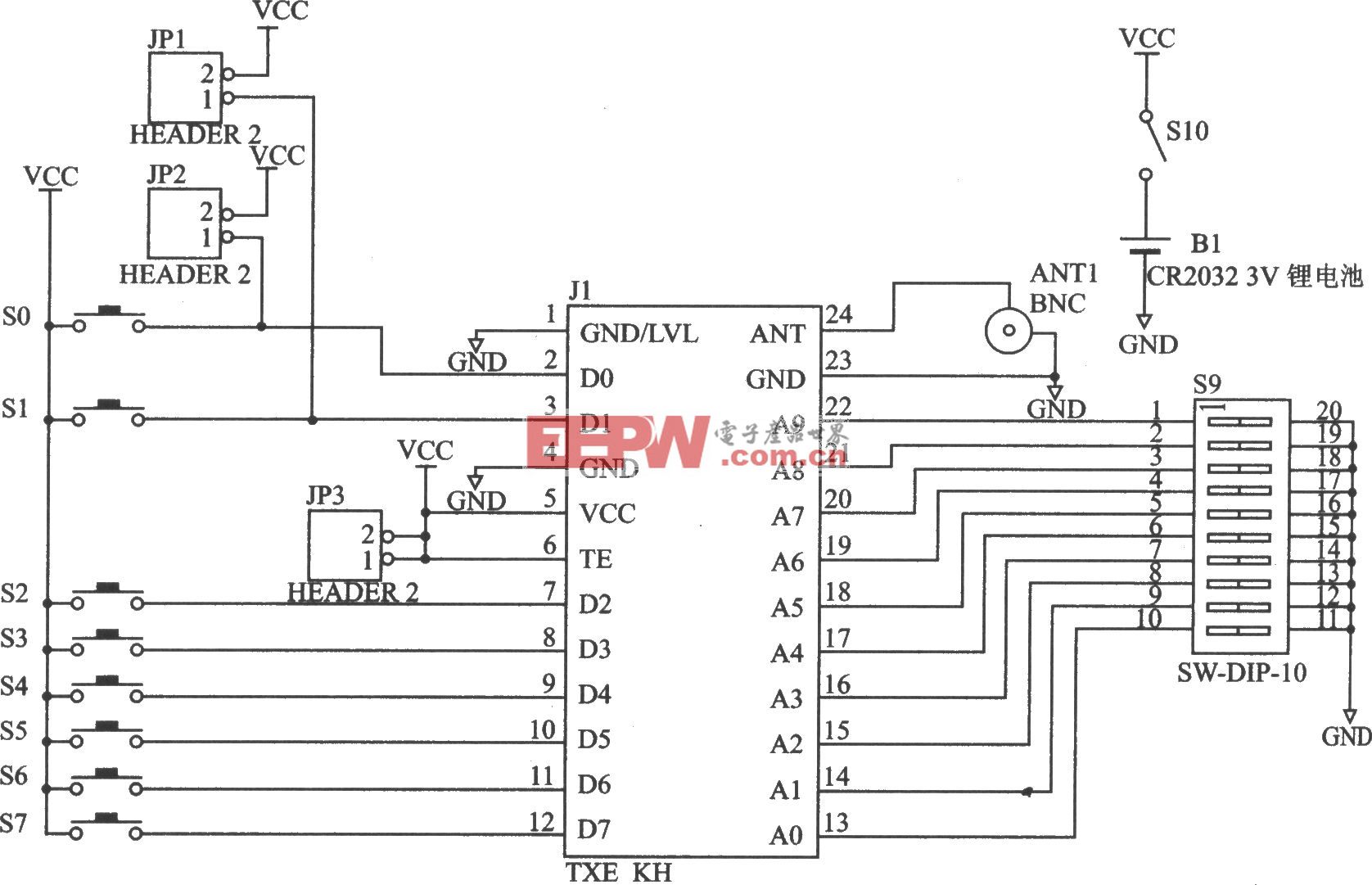

CAVLC是一種依據(jù)4×4塊變換系數(shù)的zig-zag掃描順序進行的編碼算法。塊系數(shù)的非零系數(shù)幅值較小,主要集中在低頻段,經(jīng)過zig-zag掃描后,連續(xù)零的個數(shù)較多,采用run-level游程編碼,通過編碼5個語義元素能夠?qū)崿F(xiàn)高效無損壓縮,編碼流程如圖1所示。zig-zag掃描后,順序編碼系數(shù)標記(coeff_token)。尾1的符號(trailing_ones_sign_flag)、除尾1外非零系數(shù)的級(level),最后一個非零系數(shù)前零的個數(shù)(total_zeros)和零的游程(run_before)。其中TC、T1、T0分別表示非零系數(shù)個數(shù)、尾1個數(shù)以及最后一個非零系數(shù)前零的個數(shù)。由于CAVLC編碼流程是串行的,軟件容易實現(xiàn),但執(zhí)行速度慢且效率低。

2 CAVLC編碼器硬件結(jié)構(gòu)設(shè)計

2.1 并行化編碼結(jié)構(gòu)

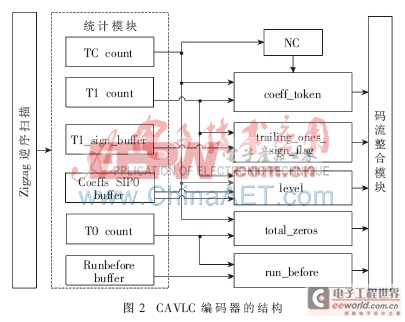

為了提高運算速度和效率,將圖1的CAVLC編碼流程并行化處理,適合FPGA實現(xiàn)。根據(jù)文獻[4]提出的思路,將CAVLC編碼分成掃描和編碼2部分,見圖2。由zig-zag逆序掃描、統(tǒng)計、編碼、碼流整合4個模塊組成。zig-zag模塊和統(tǒng)計模塊構(gòu)成掃描部分,編碼模塊和碼流整合模塊構(gòu)成編碼部分,系統(tǒng)采用狀態(tài)機控制。由于trailing_ones_sign_flag、level和run_before都是從zig-zag掃描后序列的尾部開始編碼,所以本設(shè)計中zig-zag采用逆序掃描。統(tǒng)計模塊用計數(shù)器統(tǒng)計zig-zag逆序掃描輸出序列的TC、T1和T0,將尾1符號(T1_sign)、除尾1外的非零系數(shù)(coeffs)和零的游程(runbefore)存入緩存器并輸出。編碼模塊分成6個子模塊:NC生成模塊、coeff_token模塊、trailing_ones_sign_flag模塊、level模塊、total_zeros模塊以及run_before模塊。統(tǒng)計模塊給各編碼子模塊提供輸入數(shù)據(jù),保證各編碼子模塊并行工作,減少了CAVLC編碼的時鐘周期,提高了編碼器執(zhí)行效率。由于CAVLC編碼是變長的,使得每個編碼子模塊的輸出碼流長度不確定,各編碼子模塊的碼字寄存器寬度不同。為了保證各編碼子模塊生成的碼字能夠緊湊無縫鏈接和有效存儲,在各編碼子模塊的碼字輸出中嵌入輸出標志信號和碼長信息,當輸出標志信號為高電平時碼字與碼長有效,低電平時則無效,經(jīng)碼流整合模塊整合后輸出。

評論