基于FPGA的成像聲納FFT波束形成器設計

海洋面積占地球表面積的71%,海底蘊藏的石油、天然氣等礦產資源量也遠遠超過陸地。由于能源危機和資源短缺日益嚴重,世界各國對海洋的開發利用愈發重視。水聲成像技術不僅能夠探測海底結構,而且相比于傳統視頻設備,其優點是呈現的圖像幾乎不受水文條件的影響,無論在軍用還是民用領域,聲成像技術都是未來船舶與海洋工程研究的主要技術之一[1]。

對要求實時成像的成像聲納來說,成像速度是衡量其性能優劣的一個非常重要的標準。波束形成器是成像聲納數字系統的重要組成部分,其運算速度影響到整個系統的成像速度,因此提高波束形成運算速度是提升成像聲納成像速度的關鍵。相移波束形成中的FFT波束形成技術由于具有非常成熟的算法、實現結構和快速的運算速度,成為成像聲納波束形成器首選。

1 FFT波束形成器原理

波束形成技術是指將按一定幾何形狀排列的多元基陣的各陣元輸出,經過處理形成空間指向性的方法,目的是使多陣元構成的基陣經過適當地處理得到在預定方向的指向性[2]。

本文采用等間隔直線陣FFT波束形成。一個N元等間隔直線陣陣元間隔為d,當接收信號為單頻或窄帶信號時,基陣第i號陣元的輸出信號可用復數表示為:

式(2)實際上是離散傅里葉變換的形式,因此計算一個等間隔直線陣各波束輸出值就等價于計算各陣元的輸出信號xi的離散傅里葉變換,可以利用這一特點對基陣輸出信號作快速波束形成處理。

2 FFT波束形成器的DSP Builder實現與驗證

2.1 FFT波束形成器的DSP Builder實現

為了讓成像聲納達到較高的分辨率,需要對更多的數據進行實時性處理。因此本設計要求在20 ?滋s內得到512點FFT運算結果,并且運算結果誤差在1%以內。考慮參數要求,FFT波束形成器設計包括如下三部分:數據預處理部分(加權、聚焦),512點基2 DIT-FFT算法部分及數據整理部分(ABS計算)。總體框架如圖1所示。

2.1.1 流水線技術

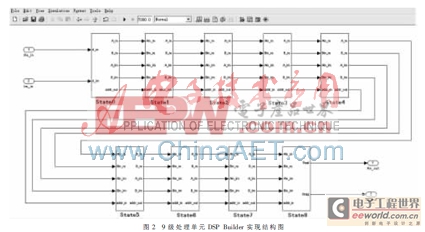

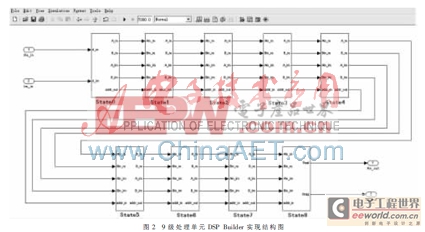

為了提高數據處理能力,采用流水線設計方法提高系統的工作頻率。FFT 模塊9級運算單元(State0~State8)并行運行,這樣9級數據運算時間僅為1級的運算時間。圖2給出了9級處理單元(State0~State8)的DSP Builder實現結構圖。

海洋面積占地球表面積的71%,海底蘊藏的石油、天然氣等礦產資源量也遠遠超過陸地。由于能源危機和資源短缺日益嚴重,世界各國對海洋的開發利用愈發重視。水聲成像技術不僅能夠探測海底結構,而且相比于傳統視頻設備,其優點是呈現的圖像幾乎不受水文條件的影響,無論在軍用還是民用領域,聲成像技術都是未來船舶與海洋工程研究的主要技術之一[1]。

對要求實時成像的成像聲納來說,成像速度是衡量其性能優劣的一個非常重要的標準。波束形成器是成像聲納數字系統的重要組成部分,其運算速度影響到整個系統的成像速度,因此提高波束形成運算速度是提升成像聲納成像速度的關鍵。相移波束形成中的FFT波束形成技術由于具有非常成熟的算法、實現結構和快速的運算速度,成為成像聲納波束形成器首選。

1 FFT波束形成器原理

波束形成技術是指將按一定幾何形狀排列的多元基陣的各陣元輸出,經過處理形成空間指向性的方法,目的是使多陣元構成的基陣經過適當地處理得到在預定方向的指向性[2]。

本文采用等間隔直線陣FFT波束形成。一個N元等間隔直線陣陣元間隔為d,當接收信號為單頻或窄帶信號時,基陣第i號陣元的輸出信號可用復數表示為:

式(2)實際上是離散傅里葉變換的形式,因此計算一個等間隔直線陣各波束輸出值就等價于計算各陣元的輸出信號xi的離散傅里葉變換,可以利用這一特點對基陣輸出信號作快速波束形成處理。

2 FFT波束形成器的DSP Builder實現與驗證

2.1 FFT波束形成器的DSP Builder實現

為了讓成像聲納達到較高的分辨率,需要對更多的數據進行實時性處理。因此本設計要求在20 ?滋s內得到512點FFT運算結果,并且運算結果誤差在1%以內。考慮參數要求,FFT波束形成器設計包括如下三部分:數據預處理部分(加權、聚焦),512點基2 DIT-FFT算法部分及數據整理部分(ABS計算)。總體框架如圖1所示。

2.1.1 流水線技術

為了提高數據處理能力,采用流水線設計方法提高系統的工作頻率。FFT 模塊9級運算單元(State0~State8)并行運行,這樣9級數據運算時間僅為1級的運算時間。圖2給出了9級處理單元(State0~State8)的DSP Builder實現結構圖。

評論