MELP語音編碼的FPGA實現的系統框架

3 MELP語音編碼的硬件構成

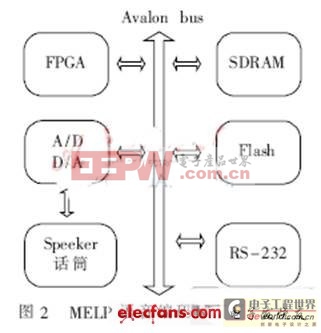

硬件電路板由Altera公司的FPGA芯片EP2C8作為主控芯片,此外還包括:8 MB容量的SDRAM、2 MB容量的Flash、WM8731音頻芯片,自帶音頻D/A、A/D,為方便調試,另帶有串口。MELP語音編碼硬件構成如圖2所示。

為便于程序的調試,擴充了RS-232串口,可與計算機串口直接互聯。8 MB容量的SDRAM可為Nios II軟核處理器運行嵌入式操作系統提供所需的存儲空間,2 MB容量的Flash也可為MELP的軟件編制提供存儲空間。WM8731音頻芯片提供快速的音頻編解碼數據碼流,并向揚聲器傳輸解碼后的數據流。

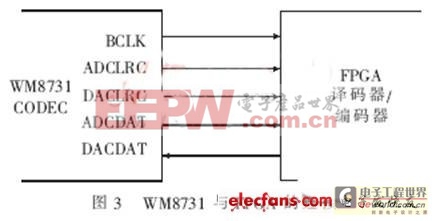

WM8731是一個低功耗的立體聲Codec芯片,內部集成了耳機放大功能,因此,WN8731也可以應用于MD、DAT等設備[7];內建了24 bit(multi-bit)Σ-Δ三角模數轉換和數模轉換,ADC和DAC都使用了超采樣數字插值技術;支持數字音頻的位數可以是16 bit~32 bit,采樣率從8 kHz~96 kHz;立體聲音頻輸出帶有數據緩存和數字音量調節,WM8731通過2~3根的串行接口進行控制,可工作于主從模式。在3.3 V信號電壓時ADC可以達到90 dB的信噪比,1. 8 V信號電壓時ADC可以達到85 dB的信噪比。3.3 V信號電壓時的DAC信噪比可以達到100 dB,1.8 V信號電壓時DAC信噪比也有95 dB。ADC和DAC的頻率響應都在8 kHz~96 kHz之間,可以有選擇地使用ADC的高通濾波。一般情況下,WM8731都是在專業聲卡領域中使用。

各芯片之間的互聯通過引線連接到FPGA的IO腳。Nios II處理器的內部總線通過定義引腳連到IO,這樣需要連接到Avavon總線的芯片可通過IO腳連到總線上。圖3所示為WM8731CODEC芯片與主芯片FPGA的連接。

串口方面,SDRAM及Flash使用Nios II自帶的基于Avalon總線的軟IP。

本文討論了MELP混合線性碼激勵的FPGA實現的硬件構成,介紹了硬件主要組成芯片及MELP編解碼的主要框架,可以用于下一步軟件程序的編制。

評論