基于FPGA的多普勒測振計(jì)信號采集與處理系統(tǒng)設(shè)計(jì)方案

2.2 FPGA邏輯設(shè)計(jì)

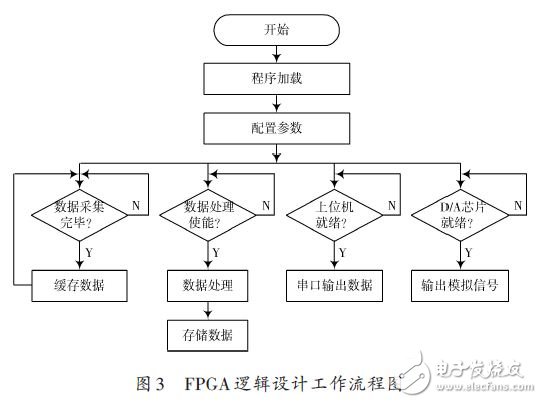

本文引用地址:http://www.czjhyjcfj.com/article/221564.htm在FPGA邏輯設(shè)計(jì)中,采用Altera公司的Quartus Ⅱ綜合開發(fā)環(huán)境對FPGA進(jìn)行設(shè)計(jì)、仿真和調(diào)試,實(shí)現(xiàn)信號的采集和處理功能,F(xiàn)PGA邏輯設(shè)計(jì)工作流程圖如圖3所示。

在工作過程中,F(xiàn)PGA首先檢測是否接收到數(shù)據(jù)采集完畢的使能信號,如果沒有接收到就一直進(jìn)行檢測,如果收到就讀取16 位數(shù)據(jù)并緩存。當(dāng)FIFO 接近全滿狀態(tài)時啟動數(shù)據(jù)處理邏輯,數(shù)據(jù)處理邏輯通過一系列乘加運(yùn)算結(jié)合流水線的設(shè)計(jì)方法實(shí)現(xiàn),并將運(yùn)算結(jié)果適當(dāng)截位輸出給雙口RAM.雙口RAM 擁有兩套完全獨(dú)立的數(shù)據(jù)線、地址線和讀寫控制線,當(dāng)檢測到有數(shù)據(jù)輸入時,讀地址開始加1,否則讀地址保持不變。上位機(jī)準(zhǔn)備就緒,即雙口RAM 數(shù)據(jù)準(zhǔn)備輸出時,雙口RAM 寫地址開始加1,通過串行接口將數(shù)據(jù)輸出。在輸出模擬信號時,只有當(dāng)DAC8551芯片輸入寄存器接收到24位數(shù)據(jù),同時同步信號為低電平時,才能啟動 D/A轉(zhuǎn)換邏輯。

下面將介紹幾個典型數(shù)字邏輯模塊的關(guān)鍵設(shè)計(jì)點(diǎn)。

(1)時鐘模塊

本設(shè)計(jì)中外部晶振提供給FPGA的時鐘為50 MHz,時鐘模塊的功能就是根據(jù)設(shè)計(jì)要求,利用鎖相環(huán)以及使能時鐘的設(shè)計(jì)方法為各個模塊提供所需的時鐘信號。通過鎖相環(huán)配置工具將50 MHz的系統(tǒng)時鐘進(jìn)行1/2分頻,從而產(chǎn)生頻率為25 MHz并滿足時序約束的主時鐘。使能時鐘設(shè)計(jì),即不增加新的時鐘,而只是利用原有主時鐘,讓分頻信號作為使能信號來使用,通過該設(shè)計(jì)對主時鐘進(jìn)行1/16 分頻,為信號處理模塊提供工作時鐘。

(2)A/D邏輯模塊

A/D 邏輯模塊的任務(wù)是根據(jù)ADS1174 的轉(zhuǎn)換時序圖,在芯片的引腳發(fā)出或接收相應(yīng)的信號,使得ADS1174完成啟動、配置和數(shù)據(jù)讀取操作。其控制操作如下:首先配置ADS1174 的相關(guān)參數(shù),包括運(yùn)行模式、接口類型等,然后通過查詢ADS1174的DRDY信號來判定數(shù)據(jù)轉(zhuǎn)換是否完成,開始讀取數(shù)據(jù),最后將讀得數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換,同時完成數(shù)據(jù)的緩存。A/D邏輯模塊每完成一次信號采樣,則等待下一次觸發(fā)脈沖的到來。

(3)數(shù)據(jù)處理模塊

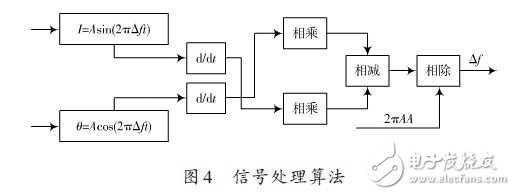

數(shù)據(jù)處理模塊的功能是提取出多普勒測振計(jì)信號中的頻移信號,本設(shè)計(jì)采用如圖4 所示的信號處理算法,通過微分和乘加運(yùn)算,同時結(jié)合流水線的設(shè)計(jì)方法來實(shí)現(xiàn)。微分運(yùn)算的處理是將前一個數(shù)據(jù)延遲一個單位時間,用當(dāng)前的數(shù)據(jù)減去前一個數(shù)據(jù)得到的。通過宏模塊構(gòu)建16 b × 16 b有符號乘法器來實(shí)現(xiàn)乘法運(yùn)算,同時為了避免溢出,對乘法運(yùn)算結(jié)果適當(dāng)截位。相關(guān)除法器操作則與乘法器類似。

電子管相關(guān)文章:電子管原理

光耦相關(guān)文章:光耦原理

fpga相關(guān)文章:fpga是什么

評論