基于FPGA與AD5422的PLC模擬量擴展單元的設計

表1列舉了模擬量輸出規格,包括量程、用戶分辨率、用戶編程的數據范圍等。

本文引用地址:http://www.czjhyjcfj.com/article/201708/363624.htm可見因為我們給PLC編程的數據和最終送給AD5422芯片的數據有一定的區別,則對于數據處理來說,我們需要完成以下幾個功能:

1)識別數據有效性:PLC給用戶1/12000的分辨率和控制字并不能占用0x0000-0xFFFF全部范圍內的數據,也就是說存在一部分的輸入數據是非法的無效的,需要在經過處理前識別出來,避免后續處理出錯,FPGA設計通過數據比較輸出數據有效或者無效判斷,當然設計可以選擇無效數據丟失或者輸出報警信號。

2)雙極性轉換:對應雙極性輸出數據中的-10~+10V的數據范圍是十六進制的0xE890到0x1770 對應十進制的-6000到+6000,而AD5422的-10V-+10V對應的數據范圍是十六進制的0x000-0xFFFF是單極性的,所以先要給雙極性的原始數據加上十進制的6000,統一輸入為十六進制的0x0000-0x2EE0,對應十進制的0-12000。

3)數據擴充:通過乘法器實現輸入數據的擴充,從給用戶的十六進制0x0000-0x2EE0需要對應轉換到十六進制0x0000-0xFFFF。特別地,對于1~5V量程來說因為輸出有個1V的基準量,在適用AD5422的0~5V量程時通過擴展到AD5422對應的0~4V量程,即十六進制的0x0000-0xCCCC,當然,這一步的處理需要在FPGA內部設計硬件乘法器,使得每個量程都能乘上響應的系數完成數據擴充工作。

4)添加偏移量:對于1~5V量程來說這個1V的基準量是始終存在的,這就需要在完成數據擴充后添加偏移量,其他量程則不需要這個偏移量的添加。

2.2 FPGA其余需要添加的功能塊還包括

1)控制字識別模塊:針對獲得的命令控制字,需要能甄別,并且分離出每個通道的量程和使能信息,在獲得合法的控制字后才能通知初始化模塊開始正常的數據運行。對于非法的控制字信息也能報錯并停機。

2)初始化模塊:在上電后初始化每一個DAC芯片,包括復位芯片,開啟菊花鏈使能,清空輸出數據寄存器等操作[1]。

3)SPI接口模塊:該模塊能自動的將處理完成的數據添加字頭地址并發送,而且能夠配合初始化模塊完成DAC的初始化工作。在完成數據發送后最好還可以自動回讀DAC的狀態信息了解DAC是否過熱,電流環開路等信息。在處理完成所有工作后,自動的提供一個幀復位信號給狀態機完成一幀數據的處理工作。

4)時鐘控狀態機:該模塊能協調每個模塊的工作順序,使這個機制在數據幀能順利工作并且自動復位。

5)通道識別模塊:對于多通道數據使用同一個數據處理線來說,要有效的識別通道,通知各模塊裝載對應的量程控制字和控制SPI模塊的菊花鏈數據裝載順序。 圖4是FPGA內部整體處理機制的結構圖。

3 FPGA仿真測試

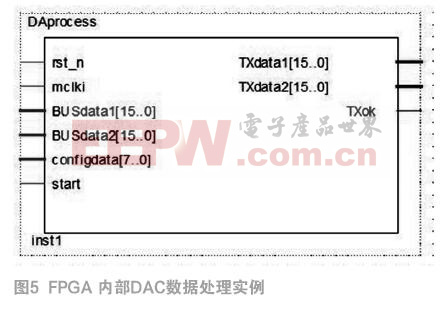

通過Verilog HDL語言編寫相關的硬件描述語言模塊,并綜合生成實例。圖5是FPGA內部實現DAC數據轉換處理的實例模塊,也是本設計的核心模塊,其相應的輸入端口包括:模塊復位rst_n;模塊主時鐘輸入mclki;通道1的總線送來的十六位數據BUSdata1[15:0];通道2的總線送來的十六位數據BUSdata2[15:0];2個DAC通道的配置數據(包括量程和使能信號)configdata[7:0] ;轉換使能信號start;相應的輸出信號包括送往SPI通信模塊發送給DAC1的數據Txdata1[15:0];發送給DAC2的數據Txdata2[15:0],以及轉換完成的使能信號TXok。

使用ModelSim軟件對FPGA內部的處理機制進行仿真測試,圖6是SPI端口對DAC進行初始化的時序仿真結果。包括發送0x560001 進行復位功能,發送0x560000 取消復位功能,發送0x550008 開啟菊花鏈使能等操作。

圖7顯示了FPGA內部數據轉換的仿真測試結果,我們先預設了DAC工作在-10~10V量程下,并在該模式下給FPGA送入十進制的6000 對應0x1770 代表要求DAC輸出正10V滿量程,計算結果輸出是有符號數的0x7FFF,說明和預期結果一致,即這部分功能模塊可以正常工作。

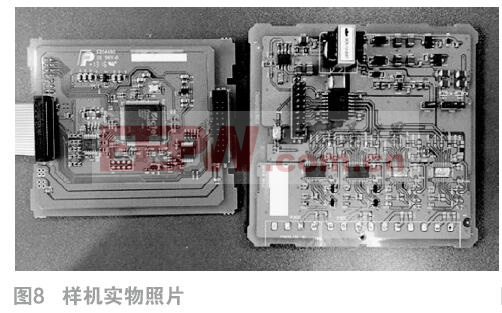

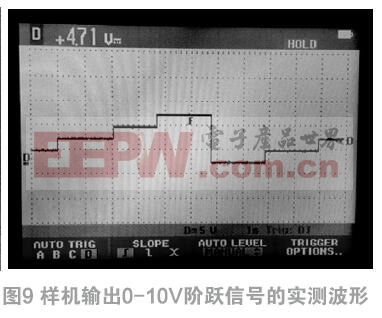

樣機測試使用Microsemi的FPGA為處理核心,使用Libero SoC開發平臺下移植了以上設計進行實體電路的運行,圖8為樣機的實物照片,左邊為頂層FPGA板,右邊為底層模擬量輸出板。其中模擬部分的硬件設計可以參考EVAL-AD5422[3]。另外,注意要做好輸出ESD保護對策。圖9顯示了該樣機輸出0~10V階躍信號的實測波形,驗證了設計的可行性,完成了相關產品的開發任務。

4 結論

本設計憑借FPGA強大的硬件可編程能力,在硬件設計方面直接省略了一顆MCU處理器及相關配套的硬件,既可以極度的精簡物料表。提升整體硬件可靠性,降低系統功耗,又不用擔心MCU會存在死機等實際運行的風險。

對于數據處理交由FPGA來實現,既可更嚴格的管理完善整體系統運行的時序。而且輸入輸出數據的關聯性更差,這樣整個設計具有更好的保密性。利用FPGA的靈活性,使電子設計能夠在很短的周期內完成[4],而且FPGA內部設計硬件乘法器,加法器等硬件模塊可以極大的提升數據處理速度,從而提升系統響應時間[5]。

參考文獻:

[1]AD5422 Datasheet[Z] Analog Devices, Inc.

[2]于笑凡,費樹岷.基于FPGA 與AD5422 的多功能信號發生器的設計[J].信息技術與信息化,2013(6): 53-55.

[3]UG-422:Evaluating the AD5422 Single Channel,16Bit,Current Source and Voltage Output DAC,HART Connectivity.[Z] Analog Devices, Inc.

[4]王玨文,金偉信,蔡一兵,等.基于FPGA的SPI總線接口的實現[J].現代電子技術,2010(14):102-104.

[5]周維龍.基于FPGA 的智能變送器的設計與開發[D].長沙:湖南大學,2010:18-22.

本文來源于《電子產品世界》2017年第9期第61頁,歡迎您寫論文時引用,并注明出處。

評論