基于Xilinx V5的DDR2數據解析功能實現

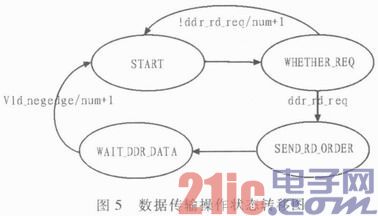

為了能夠實現4個通道數據傳輸的互不干擾,可以在程序代碼設計中使用狀態機進行控制,部分程序代碼如圖4所示,相對應的數據傳輸操作狀態轉移如圖5所示。同時只有正確接收到3個數據(脈沖周期、脈沖寬度、脈沖個數)時,脈沖才能正常的傳輸,所以需要用到兩個寄存器,第1個寄存器作為緩沖器用來接收數據,當緩沖器接收完3個數據時,將其3個數據同時發送至第2個寄存器,以控制輸出的脈沖波形。每接收到一個數據對其地址加1,以反過來讀取下一個地址的數據。

3 系統驗證結果與分析

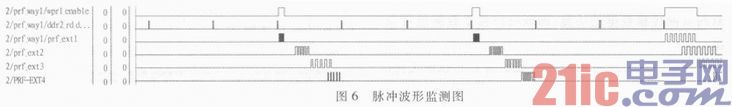

在系統驗證的過程中,一旦系統接收到發送脈沖波形的命令后,就將數據文件解析成的脈沖波形通過DDR2發送,運用Xilinx自帶的Chipscope對發送出的脈沖波形進行監測,結果如圖6所示。

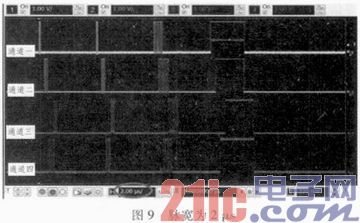

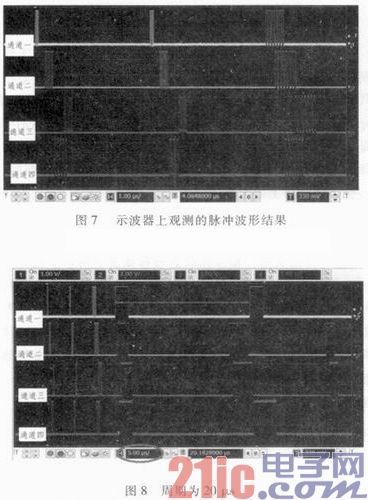

從圖6中可以看出4個通道的前3個脈沖個數分別為5,6,7,和圖2參數文件中數據的一致。通過SMA接口將波形連接到示波器上進行觀測,示波器上對應的1,2,3,4分別為第一、二、三、四通道的波形圖,觀測到的波形如圖7所示,和Chipscope上抓取的數據保持一致。為了進一步的驗證結果的正確性與否,我們以通道一為例,對其進行解釋,通過示波器引出波形,進一步驗證脈沖波形的周期和脈寬。以參數文件的00000090h:07D0h=2000d為例計算周期,2 000/100 M=20 μs,如圖8所示。以000000A0h:C8h=200d為例計算脈寬,200/100 M=2μs如圖9所示。

觀測圖形可看出通道1的周期為圖中箭頭部分的距離,為5μs×4=20μs,結果正確。

觀測圖形可看出通道1的脈寬為圖中箭頭部分的距離,為2μs,結果正確。

4 結論

文中沒計并完成了一種基于Xilinx V5的DDR2的數據解析功能的實現,了解了CPCI總線與FPGA之間的通信協議過程,同時根據外部數據文件實現了對輸出的脈沖波形進行控制,檢測到的信號波形也準確無誤,有效的控制了發射時間,在雷達應用領域中具有一定的參考價值。

評論