基于USB2_0和DDR2的數據采集系統設計與FPGA實現

4 FPGA實現

FPGA在系統設計中具有很好的靈活性和可擴展性, 因此, FPGA是一個非常好的系統實現平臺。通過對數據采集系統的資源*估, 可得出如表1所列的資源占用結果。

表1 FPGA的資源占用情況。

FPGA的資源占用情況

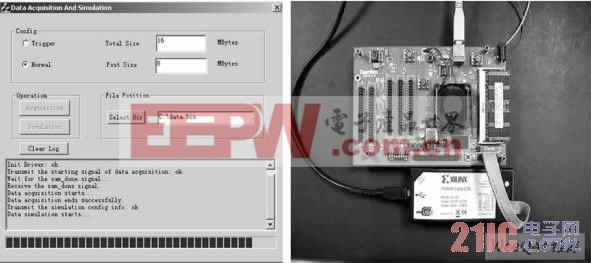

本系統最終選擇了Xilinx 公司的FPGA器件Virtex5 LX30。由于DDR2 SDRAM控制器是Xilinx公司的IP核, 故在系統的集成和實現過程中不可避免的要對原IP核進行改動, 同時, 在ISE中布局布線時, 相應地要對原有UCF文件中的約束進行修改, 以滿足時序要求。本系統除USB2.0的PHY和SDRAM外, 其余部分均由FPGA實現, 圖5所示是系統在計算機上的操作界面和實物圖。

操作界面和FPGA實物圖

圖5 操作界面和FPGA實物圖。

5 結束語

本文結合USB2.0與DDR2 SDRAM的特點, 給出了可打破普通數據采集系統在實時、高速和大容量數據采集上的瓶頸的方法, 并且在實用性方面進行了改進。該系統最終可在FPGA上實現,因為用FPGA實現具有極大的靈活性和可擴展性,并且在系統設計成本和快速實現上具有很好的競爭優勢。目前, 該數據采集系統在實際運用中效果良好。實際上, 若對采集接口稍加改進, 并將IF模塊中的乒乓緩存改為異步FIFO, 就能廣泛地應用于各類高速系統的實時數據采集。

本文引用地址:http://www.czjhyjcfj.com/article/195142.htm

評論