基于SOPC的以太網遠程數據采集系統設計

2.1 數據采集模塊

數據采集模塊包括前端信號調理電路和A/D轉換電路。前端調理主要包括傳感器、調理電路。信號調理主要實現對模擬信號的緩沖、放大,以獲得ADC所滿足的輸入信號。

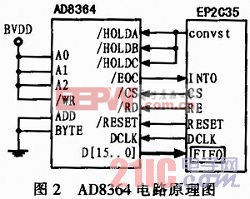

本設計采用的A/D轉化器為美國TI公司的ADS8364,ADS8364是高速、低功耗,六通道同步采樣16位并行輸出模數轉換器。采用+5 V工作電壓,當工作頻率為5 MHz時,其同步采樣為250 kHz,轉換時間4μs。六路模擬輸入分為3組(A、B和C),每個輸入端都有一個保持信號來實現所有通道的同時采樣與轉換功能,適合于多路采集系統的需要。3個保持信號(/HOLDA,/HOLDB,/HOLDC)可以啟動指定通道的轉換,當3條HOLD線均為低電平時,6個模擬輸入同時被采樣。A0、A1、A2均接高,A/D轉換結果輸出FIFO模式。A/D轉換結束后產生轉換結束信號EOC,產生中斷。在轉換結束后,將數據讀入FPGA的FIFO中。AD8364與FPGA的連接如圖2所示。本文引用地址:http://www.czjhyjcfj.com/article/193837.htm

2.2 網絡接口模塊

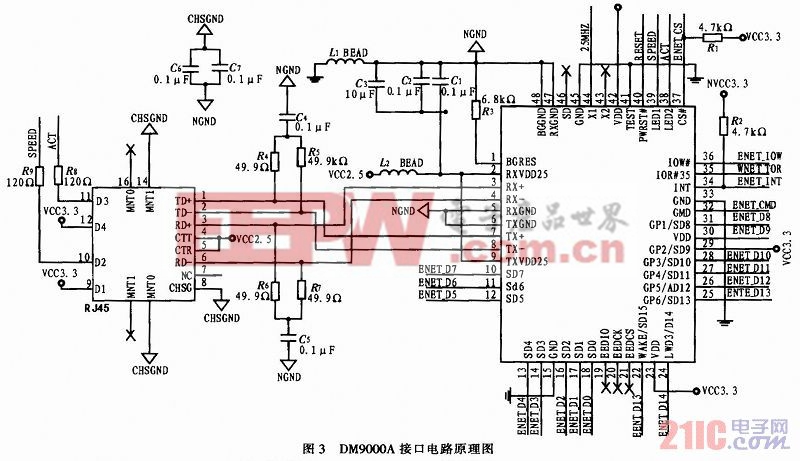

本設計的網絡芯片采用DAVICOM公司的DM9000A,該芯片具有通用處理器接口、一個10/100M PHY和4 kbytes的SRAM,是一款低功耗高性能的網絡控制器。DM9000A支持8位和16位兩種數據接口,本設計采用16位模式。其接口電路原理圖如圖3所示。

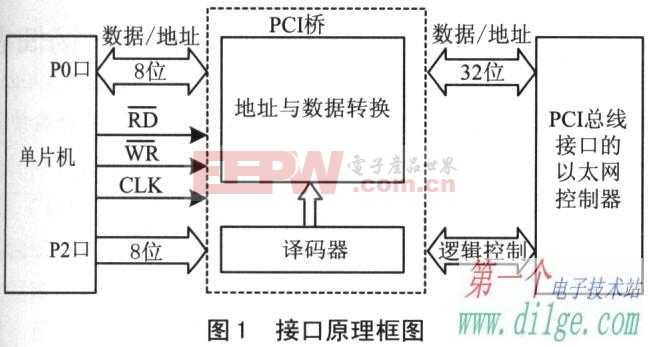

2.3 SOPC設計

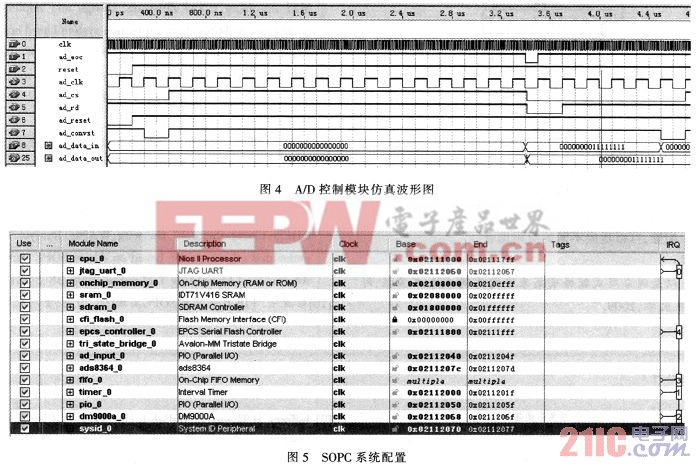

FPGA硬件設計基于Altera公司的SOPC開發環境SOPC Builder.Altera公司為SOPC工具提供了眾多的IP核支持,可以直接調用。本設計中AD控制器需要自定制,用Verilog HDL編寫控制時序與接口邏輯,采用摩爾狀態機來產生ADS8364的轉換控制信號以及FIFO讀入時鐘。其控制模塊仿真波形如圖4所示。DM900A控制器使用友晶公司的DE2開發系統中為我們提供了DM900A控制器核。

評論