基于AD7762和FPGA的數據采集系統設計

控制寄存器1的地址是0X0001,設計中控制寄存器1的內容設為0X001B。設計中通過寫控制寄存器1設置輸出數據頻率。讀時序控制A/D采樣數據的輸出。A/D的控制時序及工作狀態如圖4所示。本文引用地址:http://www.czjhyjcfj.com/article/193417.htm

為低電平期問依次將兩個寄存器的地址和內容寫入A/D中,控制A/D的工作狀態。

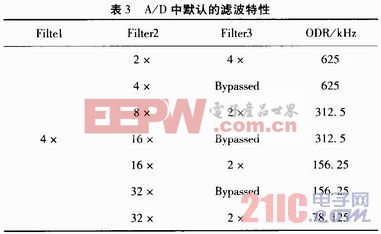

AD7762串聯了3個濾波器。通過使用不同的濾波頻率、濾波器選擇和全通的結合,可以獲得大范圍的采樣速率。通過設置寄存器1的低3位濾波器的狀態設置數據輸出速率Rate,A/D中默認的濾波特性如表3所示。

表3是在A/D內部時鐘為20 MHz時,可看出當rate=3’h3時→625 kHz;rate=3→312.5 kHz;rate=4→156.25 kHz;rate=5→78.125 kHz。

3.2 A/D讀時序控制

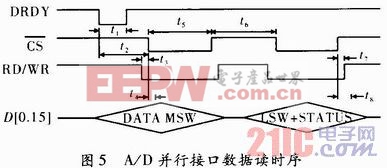

AD7762的讀時序如圖5所示。

A/D寄存器寫成功后,A/D會根據寄存器設置的工作狀態進行數據采樣和傳輸。當一個新的轉換數據結果有效時,A/D的![]() 引腳會產生一個低脈沖信號送給FPGA,當FPGA接收到這個低脈沖信號時開始接收A/D的采樣數據。由于AD7762是24位分辨率的A/D轉換器,而外部是16位數據線,所以從AD7762中讀取一個轉換結果,需要執行兩次16 bit讀數據操作。當

引腳會產生一個低脈沖信號送給FPGA,當FPGA接收到這個低脈沖信號時開始接收A/D的采樣數據。由于AD7762是24位分辨率的A/D轉換器,而外部是16位數據線,所以從AD7762中讀取一個轉換結果,需要執行兩次16 bit讀數據操作。當![]() 同時為低電平時,數據總線開始傳播數據。在二次讀操作之間,

同時為低電平時,數據總線開始傳播數據。在二次讀操作之間,![]() 必須置高一個ICLK周期的高電平。數據傳輸結束后

必須置高一個ICLK周期的高電平。數據傳輸結束后![]() 保持高電平,數據線處于高阻態,等待下一次有效數據的傳輸。

保持高電平,數據線處于高阻態,等待下一次有效數據的傳輸。

評論