基于DMA的大批量數(shù)據(jù)快速傳輸模塊設(shè)計

對于調(diào)試模式下Nios II IDE的輸出結(jié)果,如圖5所示。由于測試數(shù)據(jù)太長,這里只給出測試數(shù)據(jù)的首部及尾部。圖5(a)為測試數(shù)據(jù)的首部,使用printf()函數(shù)輸出,第一個數(shù)據(jù)為2,接著是2,3,…,從圖5(b)可看出最后一個有效數(shù)據(jù)是513,從512起的數(shù)據(jù)為0,這是數(shù)組的初始值,這與圖4相對應(yīng)。本文引用地址:http://www.czjhyjcfj.com/article/192791.htm

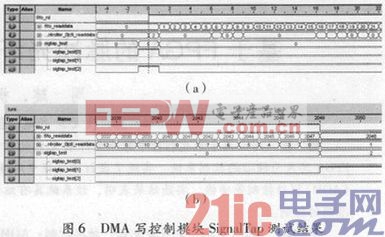

DMA寫控制模塊測試時,置FIFO數(shù)據(jù)寬度為16,NiosⅡ控制端口數(shù)據(jù)總線寬度為16,F(xiàn)IFO深度為2 048,在NiosⅡ軟件中設(shè)置一個長度為2 048的數(shù)組,數(shù)組數(shù)據(jù)寬度為16位,初始化時把數(shù)據(jù)賦值為1~2 048的計數(shù)值,然后發(fā)起DMA寫傳輸,把數(shù)據(jù)寫入到DMA寫控制模塊中,在FPGA再用硬件語言讀此外設(shè)中FIFO數(shù)據(jù)并在SignalTapⅡ中顯示,其測試結(jié)果如圖6所示。

圖6中,fifo_rd表示FPGA中硬件邏輯讀取DMA寫控制模塊的讀信號,fifo_readdata是外設(shè)中FIFO的數(shù)據(jù)總線信號,sigtap_test信號連接至外設(shè)中FIFO滿、FIFO空以及waitrequest信號(LSB),圖6(a)表示了外部邏輯讀取外設(shè)中FIFO的數(shù)據(jù)起始段,在讀信號有效之前,sigtap_ test[2]信號是高電平,表示FIFO滿,sigtap_test[0]為高,表示外設(shè)此刻不能響應(yīng)DMA寫入的數(shù)據(jù),然后FPGA外部邏輯在檢測到FIFO滿后開始讀取數(shù)據(jù),在下一個時鐘周期,F(xiàn)IFO數(shù)據(jù)總線上出現(xiàn)有效數(shù)據(jù)。圖6(b)是讀取FIFO時數(shù)據(jù)的結(jié)束段,最后一個數(shù)據(jù)為2 048,讀取后,sig tap_test[1]為高電平,表示數(shù)據(jù)讀空,這與NiesⅡ中軟件寫入DMA從而寫入DMA寫控制模塊的數(shù)據(jù)是一致的,由此驗證了模塊設(shè)計的正確性。

5 結(jié)束語

設(shè)計方案穩(wěn)定可靠、傳輸速度高,具有一定的通用性,能滿足NiosⅡ與外設(shè)之間的大批量數(shù)據(jù)傳輸,具有廣泛的應(yīng)用前景,同時,使用了FIFO作為緩存,進一步提高了數(shù)據(jù)吞吐量,具有較強的實用價值。

評論