三階高密度雙極性信號編譯碼的建模與仿真

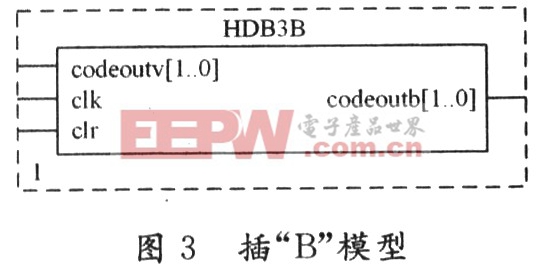

2.2 插“B”模塊的實現

建模思路是當相鄰“V”符號之間有偶數個非0符號的時候,把后一小段的第1個“O”變換成一個“B”符號。在此用一個4位的移位寄存器實現延遲作用,經插“V”處理過的碼元,在同步時鐘的作用下,同時進行是否插“B”的判決,等到碼元從移位寄存器里出來的時候,就可以決定是應該變換成“B”符號,還是照原碼輸出。輸出端用“11”表示符號“V”,“01”表示“1”碼,“00”表示“O”碼,“10”表示符號“B”,其模型如圖3所示。

2.3 單極性變雙極性的實現

根據編碼規則,“B”符號的極性與前一非零符號相反,“V”極性符號與前一非零符號一致。因此將“V”單獨拿出來進行極性變換(由前面已知“V”已經由“11”標識,相鄰“V”的極性是正負交替的),余下的“1”和“B”看成一體進行正負交替,這樣就完成了三階高密度雙極性的編碼。

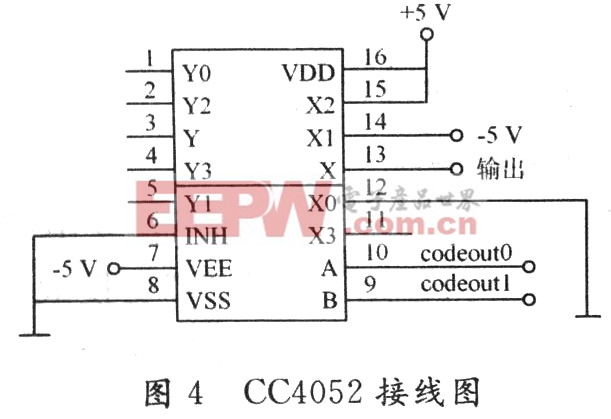

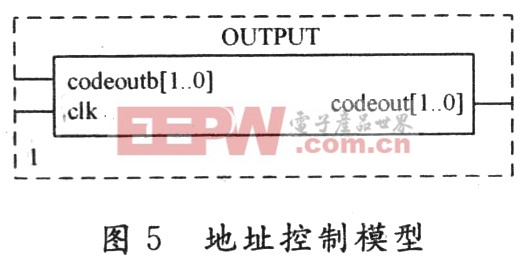

因為經過插“B”模塊后,“V”,“B”,“1”已經分別用雙相碼“11”,“10”,“01”標識,“O”用“00”標識。而在實際應用中,CPLD或FPGA端口輸出電壓只有正極性電壓,在波形仿真中也只有“+1”和“O”,而無法識別“一1”。所以要得到所需要三階高密度雙極性編碼的結果,需定義的“00,“01”,“10”來分別表示“0”,“一1”,“+1”。將插“B”模塊后輸出的“OO”,“01”,“10”,“1l”組合轉換為“00”,“01”,“10”組合表示,再通過“00”,“01”,“10”控制四選一數字開關的地址來選擇輸出通道,就可以實現O,一E,+E。在此本文用CC4052的一組通道作為四選一數字開關,將CPLD或FPGA目標芯片的標識性輸出轉換成雙極性信號,最終實現三階高密度雙極性非歸零編碼。CC4052接線如圖4所示,實現地址控制器的模型如圖5所示。

評論