20×18位符號定點乘法器的FPGA實現

1.1 Booth編碼與部分積的設計

在此采用的是基4-Booth編碼方式。在補碼表示的二進制數據中,擴展其最高位,并無影響。乘數A位寬為N,若N為奇數將A作符號擴展為A',使其位寬為偶數。設定:經過處理以后,乘數A'寬度為H,H為偶數且不得小于N。則乘數A'可表示為:

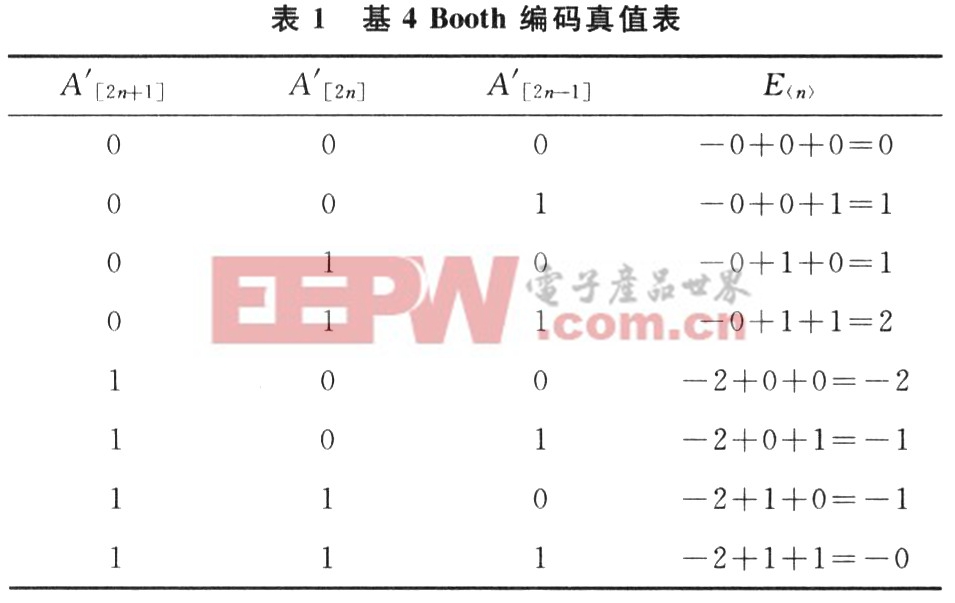

其值如表1所示:

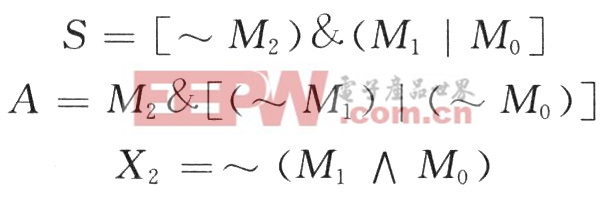

可以看到:基4布思編碼一次考慮了3位:本位、相鄰高位、相鄰低位;處理了2位,確定運算量0,1B,2B,形成(H/2)項編碼項、乘積項。對于2B的實現,只需要將B左移1位。因此,不管從那方面來說,基4算法方便又快捷。而基2算法1次只考慮2位、處理1位,形成N項編碼項、乘積項,只是方便而已。SMIC提供的O.18 vm標準單元庫中,布思編碼邏輯表達式為:

以M2指示相鄰高位,以M1指示本位,以M0指示相鄰低位。S為0時正,為1時負;A為0時操作數為0,為1時操作數為B;X2為O時操作數為0,為1時操作數為28。對于0,B,2B都比較好實現,2B=(B1);對于(-2B)實現如下:一2B=2×(-B)=[~(B1)]+1在硬件實現中,相鄰部分積之間的權相差4,也就是部分積之間錯開兩位,把加1拿出來;對于所有As為1時,把所有的加1拿出來單獨做部分積,這樣可以省去多個加法器,節省器件。對與一個18 b的乘數,可以產生9個部分積,改進此Booth編碼,再加上一個補1的數,一共產生10個加數。

1.2 4-2壓縮邏輯實現

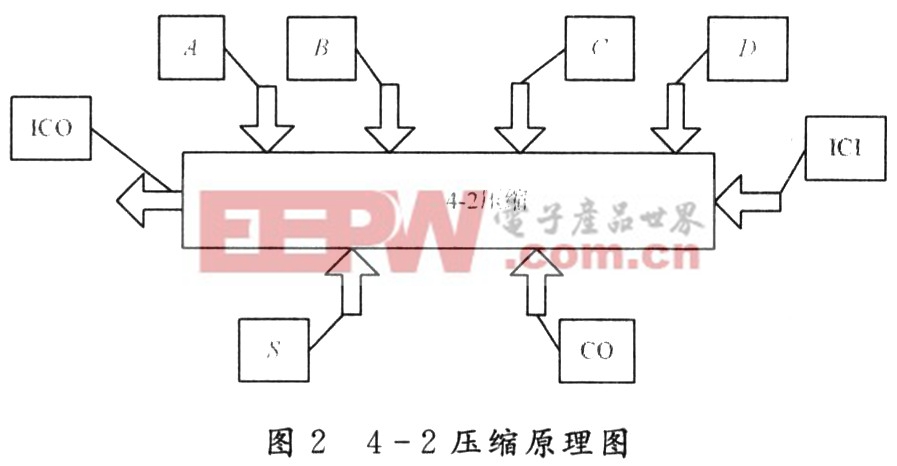

4-2壓縮原理圖如圖2所示。它有5個輸入端:A,B,C,D,ICI;三個輸出端:S,CO,ICO。將5-3編碼器并成1行,即為5-3計數行;若將相鄰低位之ICO接入本位之ICI,則成為4-2壓縮器。這樣可以減少2個操作數。5-3計數器代數運算式如下:

S+CO×2+ICO×2=A+B+C+D+ICI

即:I0,I1,I2,I3,Ci,D權值為1;C,C0權值為2。

評論