低功耗FPGA電子系統優化方法

影響FPGA功耗的因素有溫度、電壓、翻轉率等,把FPGA的功耗P和影響它的因素x看成函數關系P(x),則減少功耗就是要尋找P(x)最小值。當x代表的物理量不同時,對應P(x)的單調性也不同:x代表翻轉率時,從公式(1)得知,翻轉率與動態功耗呈線性關系,P(x)是單調遞增的,降低翻轉率能有效減少動態功耗;x代表電壓和溫度時,根據文獻[5]給出的實驗結果表明,在一定x范圍內,P(x)單調遞增,降低溫度和電壓能顯著減少漏電流。電源電壓降低5%就可以降低靜態功耗10%,不過FPGA一般只能在標準電壓的±5%幅度內調整。在實際設計中,不需要對P(x)精確建模,只要大致確定P(x)的單調區間和單調性,就能找到功耗最小點。

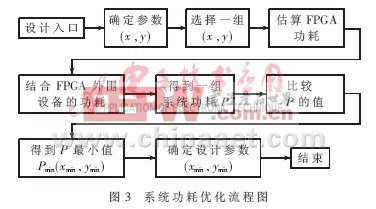

通常會遇到一些對功耗影響復雜交錯的因素,它們對功耗的影響不容易判斷。假設有2個相互關聯的功耗影響因素x、y,P(x)、P(y)都是單調遞增或單調遞減的,但x和y不能同時向著P減少的方向變化,此時功耗P的最小值需要綜合考慮x和y的取值。在P(x,y)沒有建模的情況下,可以通過對(x,y)參數取樣后樣點的P值來簡單判斷P(x,y)最小值點,也就是選定(x1,y1)、(x2,y2)…(xn,yn)后,通過比較P(x1,y1)、P(x2,y2)…P(xn,yn)的大小得出最小值Pmin(xmin,ymin)。然后將(xmin,ymin)反饋到系統設計中,便得到功耗最省的系統。

圖3所示為一種系統功耗優化方法,在系統設計時,先確定對功耗有影響的2個關聯參數x、y,在滿足系統要求的前提下,選定一系列(x,y)組合,在每個(x,y)樣點通過XPower估算FPGA的功耗,再結合從數據手冊或實驗里得到的外圍設備的功耗,可得到系統整體功耗值P(x,y),通過分析這些樣點上的系統功耗值大小,確定功耗最小點Pmin(xmin,ymin)。最后將這組參數(xmin,ymin)反饋到設計中,從而達到優化系統設計的目的。本文引用地址:http://www.czjhyjcfj.com/article/191793.htm

3 系統功耗優化實例

3.1 FPGA讀寫SRAM系統設計

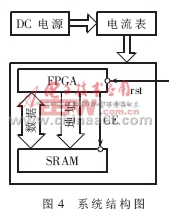

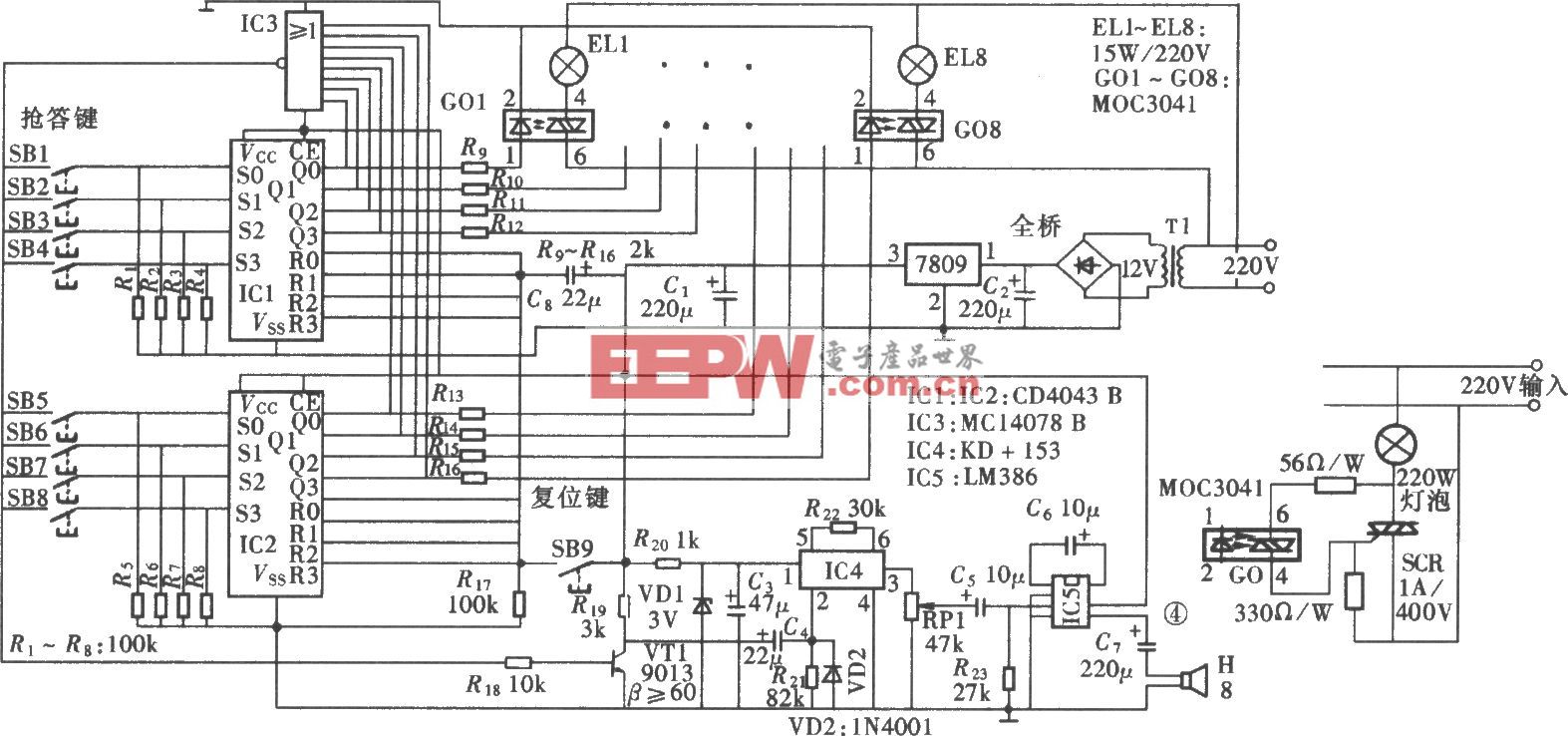

FPGA讀寫SRAM的簡單系統如圖4所示。

為了與理論值比較,要求該系統功耗為可測的。通過控制線rst和CE的電平高低來控制FPGA和SRAM工作狀態,通過測量電壓和電流可得到此時系統的功耗:當rst為低時,FPGA和SRAM都為空閑狀態,測得的功耗為PFi+PSi(PFi為FPGA在idle狀態的功耗,PSi為SRAM在idle狀態的功耗,PFw為FPGA在work狀態的功耗,PSw為SRAM在work狀態的功耗,下同);當rst為高,CE為高時,FPGA為工作狀態,SRAM為空閑狀態,測得的功耗為PFw+PSi;當rst為高,CE為低時,FPGA和SRAM都為工作狀態,測得的功耗為PFw+PSw。由SRAM數據手冊得知,PSi在?滋W量級[6]時可忽略不計,所以控制線與所測得功耗關系如表1所示。

選取讀寫頻率與讀寫時間占空比兩個因素分別做為功耗影響因素x、y,當系統數據線位寬為8 bit時,在滿足系統數據讀寫率為6 KB/s的前提下,只要x?y=6 K/s便能滿足,如(6 kHz,1)、(12 kHz,0.5)、(1 MHz,0.006)等。在理想狀態下,當整體翻轉率一樣時,功耗是一樣的,與讀寫頻率和讀寫時間占空比無關。但是實際中由于FPGA邏輯實現的差異,所以功耗會有差別,需要考慮x和y的取值來選擇一個功耗最小點。這里考慮的讀寫頻率x的范圍為0.5 MHz~9 MHz,故讀寫時間占空比y的范圍為6.7?10-4~0.012。

評論