FPGA的并行多通道激勵信號產生模塊

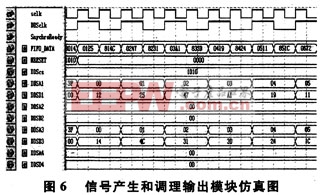

圖6為信號產生和調理輸出模塊的邏輯仿真圖,圖中DDSA1~DDSA4為6位的DDS寄存器地址總線,DDSD1~DDSD4為8位的數據總線,DDSclk為同步時鐘。通過同步設置,選擇了1、3通道輸出波形,并使DDSclk輸出串行時鐘的2分頻。從圖中可看出,此次是對1、3通道進行信號產生的控制,而沒有對2、4通道進行操作。同時將16位的FIFO_DATA控制命令譯碼后輸出,圖中FIFO_DATA的0x0125經譯碼后,選中通道1,并驅動DDSAl輸出0x01,DDSD1輸出0x25。

4 模塊測試

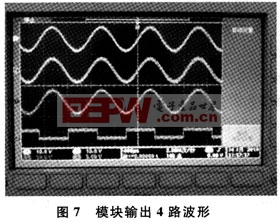

首先對各通道的信號產生電路進行單獨的測試,然后任意選擇2路通道產生獨立的激勵信號,再分別選擇3路和4路通道進行測試。進行以上測試測得模塊各通道間異步工作正常,而后進行通道同步測試。設置多通道波形產生模塊16位控制字中的a[5:0]為0x3F,進入同步設置模塊,設置通道選擇和通道輸出頻率后,對同步通道進行測試,測得同步通道模塊工作正常,滿足設計要求。

圖7為7個通道同時輸出波形的測試,其中1、2、3通道為同步方式輸出的3路正弦波,4通道為獨立輸出的方波。測試后發現,模塊具備產生高質量的并行多通道激勵信號的能力。

結 語

本文以并行多通道信號產生模型為依據,設計并實現了以FPGA為核心器件的并行多通道信號產生模塊,主要包括FPGA系統設計和多通道波形產生模塊設計。通過模塊測試后發現,該模塊具備產生高質量并行多通道激勵信號的能力。在后續的研究中,以產生各種復雜的激勵信號為主,并通過增加并行算法或采用多嵌入式軟核等方法改善模塊通道之間的并行機制,充分挖掘各通道的并行特性

評論