用FPGA解決65nm芯片設(shè)計難題

工藝尺寸縮小,連線的寬度和高度也隨之減小,對功耗有不利的影響。減小銅連線的尺寸增強了電子散射和粒子邊界效應(yīng)。從而增大了連線阻抗,導(dǎo)致電路延遲和IR壓降增大。在45nm以下,這些效應(yīng)會更加明顯。

工藝尺寸不斷縮小的結(jié)果之一是導(dǎo)致待機功耗成為芯片總功耗中的重要因素。同時,芯片用戶關(guān)心的問題從動態(tài)功耗轉(zhuǎn)向待機功耗。由于待機功耗的增大,許多通信器件分開考慮總功耗預(yù)算和待機功耗預(yù)算,并逐步增加待機功耗預(yù)算的比例。由于這些器件大部分時間處于待機模式,因此,待機功耗成為最主要的問題。

與動態(tài)功耗不同,還沒有簡單的方法來降低待機功耗。芯片開發(fā)人員不得不使用復(fù)雜的工藝和電路設(shè)計方法,犧牲晶體管速率來提高Vt,并采取延長溝道長度等措施。

目前已經(jīng)有技術(shù)突破來解決速率和待機功耗的問題。一種是應(yīng)變硅,該技術(shù)將空穴和電子對的移動能力提高了50%,從而提升了器件速率。與其它技術(shù)進步不同,應(yīng)變硅雖然提高了速率,但是并沒有增加待機功耗。然而,它必須在芯片設(shè)計中采用新的布版規(guī)則,要求較嚴(yán),導(dǎo)致了限制設(shè)計規(guī)則(RDR)這一概念的產(chǎn)生。RDR和可制造設(shè)計(DFM)在65nm以及更小工藝尺寸上越來越重要。

設(shè)計規(guī)則使開發(fā)過程越來越復(fù)雜

DFM重要性的增加以及RDR的出現(xiàn)導(dǎo)致芯片設(shè)計更加復(fù)雜。物理設(shè)計尤其需要更多的資源和簡捷的物理設(shè)計自動工具。這些規(guī)則妨礙了版層重用,增加了新技術(shù)采用硬件IP模塊的難度。結(jié)果導(dǎo)致在芯片設(shè)計上加大投入,需要更多的資源來處理新技術(shù)中的布版和設(shè)計問題。

除了越來越高的開發(fā)成本以外,芯片開發(fā)人員還面臨其它的成本難題。65nm器件僅模板成本就高達2百萬美元,而45nm器件模板成本會超過3百萬美元。理想情況下,強大的財務(wù)支持是任何業(yè)務(wù)投入的基礎(chǔ),包括芯片開發(fā)計劃等。然而,很多芯片開發(fā)項目缺乏足夠的資金支持。

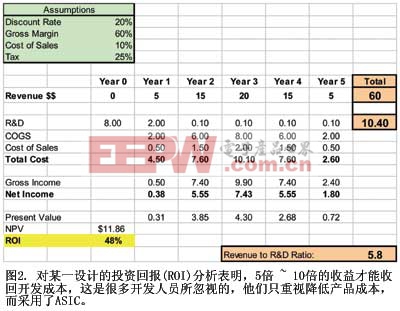

為了很好地進行財務(wù)分析,開發(fā)人員必須考慮時間、風(fēng)險、收益和成本等一系列因素。盡管這看起來很難,但可以歸結(jié)為經(jīng)過認(rèn)真設(shè)計的投資回報(ROI)分析(圖2)。在很多情況下,分析表明,產(chǎn)品生命周期的總收益應(yīng)是研發(fā)投入的5倍~10倍,這樣才能收回開發(fā)成本。簡單地看一下以收益百分比表示的研發(fā)開支(10%~20%),大部分成功的公司都會得出相同的結(jié)論。

評論