基于邏輯分析內核的FPGA電路內調試技術

使用內部邏輯分析內核也有三方面的影響。

1. 內核的尺寸限制了在大FPGA中的使用。此外由于內部FPGA存儲器用于跡線,使跡線深度很淺。

2. 設計工程師必須放棄把內部存儲器用于調試,存儲器會由所作的設計使用。

3. 內部邏輯分析儀只工作于狀態模式。它們捕獲的數據與規定的時鐘同步,而不能提供信號定時關系。

混合技術

一些FPGA廠商已開始與傳統邏輯分析儀廠商聯合開發組合技術(見圖 3)。例如Agilent 和 Xilinx 最近聯合為Xilinx的ChipScope開發2M狀態深存儲器。

混合內部和傳統邏輯分析的第一個例子是Agilent 和 Xilinx聯合為ChipScopePro開發的深存儲器,通過TDM復用能把引腳數減到最少本文引用地址:http://www.czjhyjcfj.com/article/191390.htm

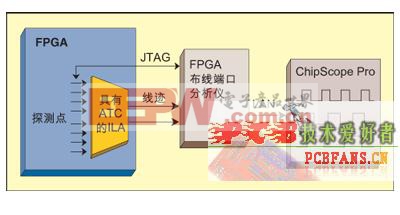

圖3: 混合內部和傳統邏輯分析的第一個例子是Agilent 和 Xilinx聯合為ChipScopePro開發的深存儲器,通過TDM復用能把引腳數減到最少。

這一解決方案把內部邏輯分析內核用于觸發。在滿足內核的觸發條件時,內核把跡線信息從經路由的結點傳送到內核,再送到引腳。引腳通過 mictor連接器接到一個小的外部跟蹤盒。該解決方案融入了TDM復用,以減少調試專用引腳數。根據內部電路的速度,復用壓縮可能是1:1,2:1或 4:1。由于跡線未在內部保存,因此IP內核要小于帶跡線存儲器的邏輯分析IP。

如何作出決定?

傳統邏輯分析和基于內核的邏輯分析技術都很有用。在選擇最適合您調試需要的方案時,事先考慮一些因素將能幫助您作出決定。下面這幾個問題能幫助您確定哪種方案最為有效。

1. 您預計會遇到哪種類型的調試問題?用內部邏輯分析儀能找到較簡單的問題,而傳統邏輯分析儀則能勝任復雜的故障。

2. 除了狀態模式外,您還需要捕獲定時信息嗎?如果需要,傳統邏輯分析儀能適應這一要求。

3. 需要多深的跡線?傳統邏輯分析儀可在各通道上捕獲達64M的跡線,而內部邏輯分析內核更適合淺的跡線。

4. 有多少引腳可專門用于調試?引腳數越少,使用內部邏輯分析儀就越適合。

5. 必須為新工具投入多少資金?雖然32通道傳統邏輯分析儀的起價為$6K,但內部邏輯分析儀及相隨波形觀察器的起價還不到$1K。

6. 研制組能容忍對FPGA設計的沖擊嗎?內核只能在大的 FPGA上工作,并會改變設計的定時。對所有尺寸和類型的FPGA,傳統邏輯分析儀的路由信號輸出對設計和工作的影響甚微。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論