基于FPGA的IEEE-1394b雙向數據傳輸系統設計

(2)1394設備發起的異步傳輸。

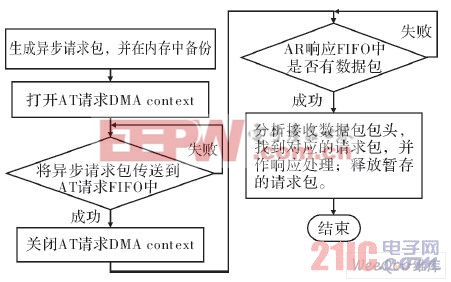

同樣,由1394設備發起的異步傳輸即由1394設備發出異步傳輸請求,主機進行響應。因此,這一部分主要是異步請求包的發送以及異步響應包的接收,其工作流程如圖3所示。這時會產生異步請求輸出DMA中斷,這可由鏈路層芯片中斷寄存器的reqTxComplete位表征。1394設備接收到主機發來的異步響應包后,會產生異步接收響應中斷,這可通過鏈路層芯片中斷寄存器得知。另外,發送出去的請求包也將被暫時存放在內存中,以便與返回的響應包對應。

圖3 1394設備發起的異步傳輸的工作流程

(3)等時傳輸。

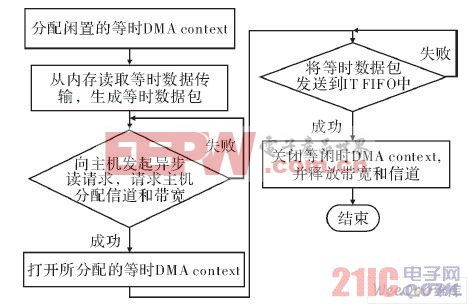

等時傳輸主要實現的功能是通過1394設備將外部的視頻數據等時傳輸到主機進行實時顯示。外部視頻數據與FPGA的SPI接口相連,FPGA把接收到的數據緩存在SRAM中,等時傳輸時,FPGA讀取SRAM中的數據,生成等時數據包。這一部分的主要工作就是等時數據包的發送,其工作流程如圖4所示。

圖4 等時傳輸的工作流程

4 測試結果分析

為了測試系統性能,進行了最快傳輸速度測試。設置總線傳輸速度為800Mb·s-1,根據1394總線協議的規定,每個數據包最大為4 096 bit。理論上一個傳輸周期125μs傳送一個數據包,因此每秒最多傳輸數據31.25 Mb,轉換為比特率,最大傳輸速度為250 Mb·s-1。實測的最快傳輸速度可達227 Mb·s-1,相對于1394a理論上的最大速度125 Mb·s-1提高了較多,因此該系統在傳輸速度上具有較大優勢。同時,主機端實時顯示的視頻實時性和可靠性也較好。

5 結束語

本系統,采用800 Mb·s-1的總線傳輸速率,利用FPGA內嵌的NIOSII處理器作為控制核心,實現了雙向傳輸,用異步傳輸方式傳輸主機端指令和攝像頭方位及狀態信息,用等時傳輸方式將攝像頭數據傳輸到主機端進行實時顯示。實驗表明,相對于1394a,該方案具有高速通信、可靠性高、實時性強等優點,達到了預定目標,運行良好。本系統研究的是1394設備與主機間的通信,在此基礎上還可以研究在脫離計算機的環境下,兩個1394設備間的通信傳輸以及多個設備的組網傳輸。

評論